target Directory Reference

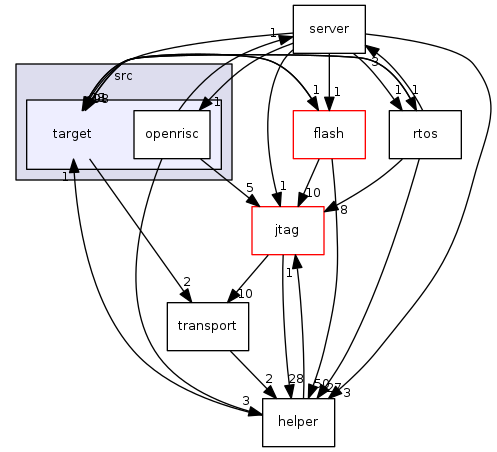

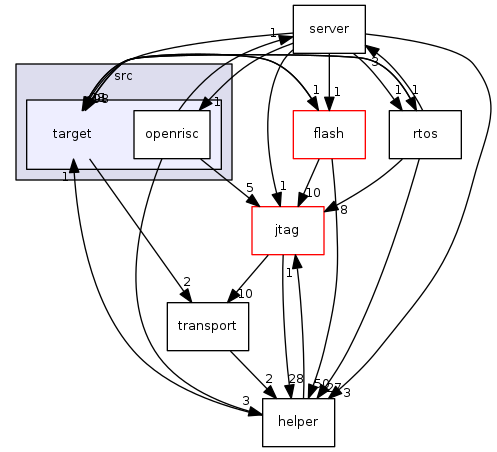

Directory dependency graph for target:

Directories | |

| directory | espressif |

| directory | openrisc |

| directory | riscv |

| directory | xtensa |

|

OpenOCD

|

Directories | |

| directory | espressif |

| directory | openrisc |

| directory | riscv |

| directory | xtensa |