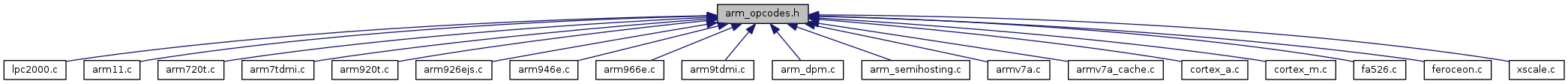

Macros used to generate various ARM or Thumb opcodes. More...

Go to the source code of this file.

Macros | |

| #define | A_FLAG 4 |

| #define | ARM_T2_CPSID(_if) |

| #define | ARM_T2_CPSIE(_if) |

| #define | ARM_T2_MRS(rd, sysm) ((0xF3EF) | ((0x8000 | (rd << 8) | sysm) << 16)) |

| #define | ARM_T2_MSR(sysm, rn) ((0xF380 | (rn << 8)) | ((0x8800 | sysm) << 16)) |

| #define | ARMV4_5_B(im, l) (0xea000000 | (im) | ((l) << 24)) |

| #define | ARMV4_5_BX(rm) (0xe12fff10 | (rm)) |

| #define | ARMV4_5_LDC(p, u, d, w, cp, crd, rn, imm) |

| #define | ARMV4_5_LDMIA(rn, list, s, w) (0xe8900000 | ((s) << 22) | ((w) << 21) | ((rn) << 16) | (list)) |

| #define | ARMV4_5_LDR(rd, rn) (0xe5900000 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_LDRB_IP(rd, rn) (0xe4d00001 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_LDRH_IP(rd, rn) (0xe0d000b2 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_LDRW_IP(rd, rn) (0xe4900004 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_MCR(cp, op1, rd, crn, crm, op2) |

| #define | ARMV4_5_MRC(cp, op1, rd, crn, crm, op2) |

| #define | ARMV4_5_MRS(rn, r) (0xe10f0000 | ((r) << 22) | ((rn) << 12)) |

| #define | ARMV4_5_MSR_GP(rm, field, r) (0xe120f000 | (rm) | ((field) << 16) | ((r) << 22)) |

| #define | ARMV4_5_MSR_IM(im, rotate, field, r) (0xe320f000 | (im) | ((rotate) << 8) | ((field) << 16) | ((r) << 22)) |

| #define | ARMV4_5_NOP (0xe1a08008) |

| #define | ARMV4_5_STC(p, u, d, w, cp, crd, rn, imm) |

| #define | ARMV4_5_STMIA(rn, list, s, w) (0xe8800000 | ((s) << 22) | ((w) << 21) | ((rn) << 16) | (list)) |

| #define | ARMV4_5_STR(rd, rn) (0xe5800000 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_STRB_IP(rd, rn) (0xe4c00001 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_STRH_IP(rd, rn) (0xe0c000b2 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_STRW_IP(rd, rn) (0xe4800004 | ((rd) << 12) | ((rn) << 16)) |

| #define | ARMV4_5_T_B(imm) |

| #define | ARMV4_5_T_BX(rm) |

| #define | ARMV4_5_T_LDMIA(rn, list) |

| #define | ARMV4_5_T_LDR(rd, rn) |

| #define | ARMV4_5_T_LDR_PCREL(rd) |

| #define | ARMV4_5_T_MOV(rd, rm) |

| #define | ARMV4_5_T_MOV_IM(rd, im) |

| #define | ARMV4_5_T_NOP (0x46c0 | (0x46c0 << 16)) |

| #define | ARMV4_5_T_STR(rd, rn) |

| #define | ARMV4_5_VMOV(op, rt2, rt, m, vm) |

| #define | ARMV4_5_VMRS(rt) (0xeef10a10 | ((rt) << 12)) |

| #define | ARMV4_5_VMSR(rt) (0xeee10a10 | ((rt) << 12)) |

| #define | ARMV5_BKPT(im) (0xe1200070 | ((im & 0xfff0) << 4) | (im & 0xf)) |

| #define | ARMV5_T_BKPT(im) |

| #define | F_FLAG 1 |

| #define | I_FLAG 2 |

Detailed Description

Macros used to generate various ARM or Thumb opcodes.

Definition in file arm_opcodes.h.

Macro Definition Documentation

◆ A_FLAG

| #define A_FLAG 4 |

Definition at line 316 of file arm_opcodes.h.

◆ ARM_T2_CPSID

| #define ARM_T2_CPSID | ( | _if | ) |

Definition at line 319 of file arm_opcodes.h.

◆ ARM_T2_CPSIE

| #define ARM_T2_CPSIE | ( | _if | ) |

Definition at line 322 of file arm_opcodes.h.

◆ ARM_T2_MRS

| #define ARM_T2_MRS | ( | rd, | |

| sysm | |||

| ) | ((0xF3EF) | ((0x8000 | (rd << 8) | sysm) << 16)) |

Definition at line 300 of file arm_opcodes.h.

◆ ARM_T2_MSR

| #define ARM_T2_MSR | ( | sysm, | |

| rn | |||

| ) | ((0xF380 | (rn << 8)) | ((0x8800 | sysm) << 16)) |

Definition at line 308 of file arm_opcodes.h.

◆ ARMV4_5_B

| #define ARMV4_5_B | ( | im, | |

| l | |||

| ) | (0xea000000 | (im) | ((l) << 24)) |

Definition at line 117 of file arm_opcodes.h.

◆ ARMV4_5_BX

| #define ARMV4_5_BX | ( | rm | ) | (0xe12fff10 | (rm)) |

Definition at line 122 of file arm_opcodes.h.

◆ ARMV4_5_LDC

| #define ARMV4_5_LDC | ( | p, | |

| u, | |||

| d, | |||

| w, | |||

| cp, | |||

| crd, | |||

| rn, | |||

| imm | |||

| ) |

Definition at line 174 of file arm_opcodes.h.

◆ ARMV4_5_LDMIA

| #define ARMV4_5_LDMIA | ( | rn, | |

| list, | |||

| s, | |||

| w | |||

| ) | (0xe8900000 | ((s) << 22) | ((w) << 21) | ((rn) << 16) | (list)) |

Definition at line 42 of file arm_opcodes.h.

◆ ARMV4_5_LDR

| #define ARMV4_5_LDR | ( | rd, | |

| rn | |||

| ) | (0xe5900000 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 64 of file arm_opcodes.h.

◆ ARMV4_5_LDRB_IP

| #define ARMV4_5_LDRB_IP | ( | rd, | |

| rn | |||

| ) | (0xe4d00001 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 93 of file arm_opcodes.h.

◆ ARMV4_5_LDRH_IP

| #define ARMV4_5_LDRH_IP | ( | rd, | |

| rn | |||

| ) | (0xe0d000b2 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 87 of file arm_opcodes.h.

◆ ARMV4_5_LDRW_IP

| #define ARMV4_5_LDRW_IP | ( | rd, | |

| rn | |||

| ) | (0xe4900004 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 81 of file arm_opcodes.h.

◆ ARMV4_5_MCR

| #define ARMV4_5_MCR | ( | cp, | |

| op1, | |||

| rd, | |||

| crn, | |||

| crm, | |||

| op2 | |||

| ) |

Definition at line 198 of file arm_opcodes.h.

◆ ARMV4_5_MRC

| #define ARMV4_5_MRC | ( | cp, | |

| op1, | |||

| rd, | |||

| crn, | |||

| crm, | |||

| op2 | |||

| ) |

Definition at line 186 of file arm_opcodes.h.

◆ ARMV4_5_MRS

| #define ARMV4_5_MRS | ( | rn, | |

| r | |||

| ) | (0xe10f0000 | ((r) << 22) | ((rn) << 12)) |

Definition at line 52 of file arm_opcodes.h.

◆ ARMV4_5_MSR_GP

| #define ARMV4_5_MSR_GP | ( | rm, | |

| field, | |||

| r | |||

| ) | (0xe120f000 | (rm) | ((field) << 16) | ((r) << 22)) |

Definition at line 72 of file arm_opcodes.h.

◆ ARMV4_5_MSR_IM

| #define ARMV4_5_MSR_IM | ( | im, | |

| rotate, | |||

| field, | |||

| r | |||

| ) | (0xe320f000 | (im) | ((rotate) << 8) | ((field) << 16) | ((r) << 22)) |

Definition at line 74 of file arm_opcodes.h.

◆ ARMV4_5_NOP

| #define ARMV4_5_NOP (0xe1a08008) |

Definition at line 46 of file arm_opcodes.h.

◆ ARMV4_5_STC

| #define ARMV4_5_STC | ( | p, | |

| u, | |||

| d, | |||

| w, | |||

| cp, | |||

| crd, | |||

| rn, | |||

| imm | |||

| ) |

Definition at line 159 of file arm_opcodes.h.

◆ ARMV4_5_STMIA

| #define ARMV4_5_STMIA | ( | rn, | |

| list, | |||

| s, | |||

| w | |||

| ) | (0xe8800000 | ((s) << 22) | ((w) << 21) | ((rn) << 16) | (list)) |

Definition at line 33 of file arm_opcodes.h.

◆ ARMV4_5_STR

| #define ARMV4_5_STR | ( | rd, | |

| rn | |||

| ) | (0xe5800000 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 58 of file arm_opcodes.h.

◆ ARMV4_5_STRB_IP

| #define ARMV4_5_STRB_IP | ( | rd, | |

| rn | |||

| ) | (0xe4c00001 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 111 of file arm_opcodes.h.

◆ ARMV4_5_STRH_IP

| #define ARMV4_5_STRH_IP | ( | rd, | |

| rn | |||

| ) | (0xe0c000b2 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 105 of file arm_opcodes.h.

◆ ARMV4_5_STRW_IP

| #define ARMV4_5_STRW_IP | ( | rd, | |

| rn | |||

| ) | (0xe4800004 | ((rd) << 12) | ((rn) << 16)) |

Definition at line 99 of file arm_opcodes.h.

◆ ARMV4_5_T_B

| #define ARMV4_5_T_B | ( | imm | ) |

Definition at line 284 of file arm_opcodes.h.

◆ ARMV4_5_T_BX

| #define ARMV4_5_T_BX | ( | rm | ) |

Definition at line 277 of file arm_opcodes.h.

◆ ARMV4_5_T_LDMIA

| #define ARMV4_5_T_LDMIA | ( | rn, | |

| list | |||

| ) |

Definition at line 239 of file arm_opcodes.h.

◆ ARMV4_5_T_LDR

| #define ARMV4_5_T_LDR | ( | rd, | |

| rn | |||

| ) |

Definition at line 231 of file arm_opcodes.h.

◆ ARMV4_5_T_LDR_PCREL

| #define ARMV4_5_T_LDR_PCREL | ( | rd | ) |

Definition at line 246 of file arm_opcodes.h.

◆ ARMV4_5_T_MOV

| #define ARMV4_5_T_MOV | ( | rd, | |

| rm | |||

| ) |

Definition at line 254 of file arm_opcodes.h.

◆ ARMV4_5_T_MOV_IM

| #define ARMV4_5_T_MOV_IM | ( | rd, | |

| im | |||

| ) |

Definition at line 270 of file arm_opcodes.h.

◆ ARMV4_5_T_NOP

| #define ARMV4_5_T_NOP (0x46c0 | (0x46c0 << 16)) |

Definition at line 264 of file arm_opcodes.h.

◆ ARMV4_5_T_STR

| #define ARMV4_5_T_STR | ( | rd, | |

| rn | |||

| ) |

Definition at line 223 of file arm_opcodes.h.

◆ ARMV4_5_VMOV

| #define ARMV4_5_VMOV | ( | op, | |

| rt2, | |||

| rt, | |||

| m, | |||

| vm | |||

| ) |

Definition at line 134 of file arm_opcodes.h.

◆ ARMV4_5_VMRS

| #define ARMV4_5_VMRS | ( | rt | ) | (0xeef10a10 | ((rt) << 12)) |

Definition at line 141 of file arm_opcodes.h.

◆ ARMV4_5_VMSR

| #define ARMV4_5_VMSR | ( | rt | ) | (0xeee10a10 | ((rt) << 12)) |

Definition at line 146 of file arm_opcodes.h.

◆ ARMV5_BKPT

| #define ARMV5_BKPT | ( | im | ) | (0xe1200070 | ((im & 0xfff0) << 4) | (im & 0xf)) |

Definition at line 205 of file arm_opcodes.h.

◆ ARMV5_T_BKPT

| #define ARMV5_T_BKPT | ( | im | ) |

Definition at line 291 of file arm_opcodes.h.

◆ F_FLAG

| #define F_FLAG 1 |

Definition at line 318 of file arm_opcodes.h.

◆ I_FLAG

| #define I_FLAG 2 |

Definition at line 317 of file arm_opcodes.h.