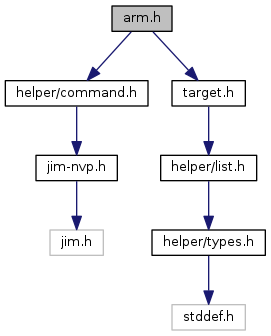

Holds the interface to ARM cores. More...

Go to the source code of this file.

Data Structures | |

| struct | arm |

| Represents a generic ARM core, with standard application registers. More... | |

| struct | arm_algorithm |

| struct | arm_reg |

Macros | |

| #define | ARM_COMMON_MAGIC 0x0A450A45U |

Functions | |

| int | arm_arch_state (struct target *target) |

| int | arm_blank_check_memory (struct target *target, struct target_memory_check_block *blocks, int num_blocks, uint8_t erased_value) |

| Runs ARM code in the target to check whether a memory block holds all ones. More... | |

| struct reg_cache * | arm_build_reg_cache (struct target *target, struct arm *arm) |

| int | arm_checksum_memory (struct target *target, target_addr_t address, uint32_t count, uint32_t *checksum) |

| Runs ARM code in the target to calculate a CRC32 checksum. More... | |

| void | arm_free_reg_cache (struct arm *arm) |

| const char * | arm_get_gdb_arch (struct target *target) |

| int | arm_get_gdb_reg_list (struct target *target, struct reg **reg_list[], int *reg_list_size, enum target_register_class reg_class) |

| int | arm_init_arch_info (struct target *target, struct arm *arm) |

| const char * | arm_mode_name (unsigned psr_mode) |

| Map PSR mode bits to the name of an ARM processor operating mode. More... | |

| struct reg * | arm_reg_current (struct arm *arm, unsigned regnum) |

| Returns handle to the register currently mapped to a given number. More... | |

| void | arm_set_cpsr (struct arm *arm, uint32_t cpsr) |

| Configures host-side ARM records to reflect the specified CPSR. More... | |

| int | armv4_5_run_algorithm (struct target *target, int num_mem_params, struct mem_param *mem_params, int num_reg_params, struct reg_param *reg_params, target_addr_t entry_point, target_addr_t exit_point, int timeout_ms, void *arch_info) |

| int | armv4_5_run_algorithm_inner (struct target *target, int num_mem_params, struct mem_param *mem_params, int num_reg_params, struct reg_param *reg_params, uint32_t entry_point, uint32_t exit_point, int timeout_ms, void *arch_info, int(*run_it)(struct target *target, uint32_t exit_point, int timeout_ms, void *arch_info)) |

| struct reg_cache * | armv8_build_reg_cache (struct target *target) |

| Builds cache of architecturally defined registers. More... | |

| const char * | armv8_get_gdb_arch (struct target *target) |

| int | armv8_get_gdb_reg_list (struct target *target, struct reg **reg_list[], int *reg_list_size, enum target_register_class reg_class) |

| struct reg * | armv8_reg_current (struct arm *arm, unsigned regnum) |

| static bool | is_arm (struct arm *arm) |

| bool | is_arm_mode (unsigned psr_mode) |

| Return true iff the parameter denotes a valid ARM processor mode. More... | |

| static struct arm * | target_to_arm (struct target *target) |

| Convert target handle to generic ARM target state handle. More... | |

Variables | |

| const struct command_registration | arm_all_profiles_command_handlers [] |

| const struct command_registration | arm_command_handlers [] |

Detailed Description

Holds the interface to ARM cores.

At this writing, only "classic ARM" cores built on the ARMv4 register and mode model are supported. The Thumb2-only microcontroller profile support has not yet been integrated, affecting Cortex-M parts.

Definition in file arm.h.

Macro Definition Documentation

◆ ARM_COMMON_MAGIC

Enumeration Type Documentation

◆ anonymous enum

| anonymous enum |

◆ arm_arch

| enum arm_arch |

◆ arm_core_type

| enum arm_core_type |

Indicates what registers are in the ARM state core register set.

- ARM_CORE_TYPE_STD indicates the standard set of 37 registers, seen on for example ARM7TDMI cores.

- ARM_CORE_TYPE_SEC_EXT indicates core has security extensions, thus three more registers are shadowed for "Secure Monitor" mode.

- ARM_CORE_TYPE_VIRT_EXT indicates core has virtualization extensions and also security extensions. Additional shadowed registers for "Secure Monitor" and "Hypervisor" modes.

- ARM_CORE_TYPE_M_PROFILE indicates a microcontroller profile core, which only shadows SP.

| Enumerator | |

|---|---|

| ARM_CORE_TYPE_STD | |

| ARM_CORE_TYPE_SEC_EXT | |

| ARM_CORE_TYPE_VIRT_EXT | |

| ARM_CORE_TYPE_M_PROFILE | |

◆ arm_mode

| enum arm_mode |

Represent state of an ARM core.

Most numbers match the five low bits of the *PSR registers on "classic ARM" processors, which build on the ARMv4 processor modes and register set.

ARM_MODE_ANY is a magic value, often used as a wildcard.

Only the microcontroller cores (ARMv6-M, ARMv7-M) support ARM_MODE_THREAD, ARM_MODE_USER_THREAD, and ARM_MODE_HANDLER. Those are the only modes they support.

◆ arm_state

| enum arm_state |

◆ arm_vfp_version

| enum arm_vfp_version |

Function Documentation

◆ arm_arch_state()

| int arm_arch_state | ( | struct target * | target | ) |

Definition at line 782 of file armv4_5.c.

References ARM_COMMON_MAGIC, arm_mode_name(), arm_state_strings, buf_get_u32(), arm::common_magic, arm::core_mode, arm::core_state, arm::cpsr, debug_reason_name(), ERROR_FAIL, ERROR_OK, semihosting::hit_fileio, semihosting::is_active, semihosting::is_fileio, LOG_ERROR, LOG_USER, arm::pc, target::semihosting, target_to_arm(), and reg::value.

Referenced by arm11_arch_state(), arm720t_arch_state(), arm920t_arch_state(), arm926ejs_arch_state(), armv7a_arch_state(), and xscale_arch_state().

◆ arm_blank_check_memory()

| int arm_blank_check_memory | ( | struct target * | target, |

| struct target_memory_check_block * | blocks, | ||

| int | num_blocks, | ||

| uint8_t | erased_value | ||

| ) |

Runs ARM code in the target to check whether a memory block holds all ones.

NOR flash which has been erased, and thus may be written, holds all ones.

Definition at line 1595 of file armv4_5.c.

References working_area::address, arm::arch, ARM_ARCH_V4, ARM_COMMON_MAGIC, ARM_MODE_SVC, ARM_STATE_ARM, ARRAY_SIZE, buf_get_u32(), buf_set_u32(), arm_algorithm::common_magic, arm_algorithm::core_mode, arm_algorithm::core_state, destroy_reg_param(), ERROR_FAIL, ERROR_OK, init_reg_param(), le_to_h_u32(), LOG_ERROR, NULL, PARAM_IN_OUT, PARAM_OUT, target_memory_check_block::result, size, target_alloc_working_area(), target_free_working_area(), target_run_algorithm(), target_to_arm(), and target_write_u32().

◆ arm_build_reg_cache()

Definition at line 646 of file armv4_5.c.

References reg::arch_info, arm_reg::arm, arm_core_regs, ARM_CORE_TYPE_SEC_EXT, ARM_CORE_TYPE_VIRT_EXT, ARM_MODE_HYP, ARM_MODE_MON, arm_reg_type, ARM_VFP_V3, arm_vfp_v3_regs, arm::arm_vfp_version, ARMV4_5_CPSR, ARRAY_SIZE, reg::caller_save, cookie, arm::core_cache, arm::core_type, arm::cpsr, reg::exist, reg::feature, reg::group, arm_reg::mode, mode, reg_feature::name, reg::name, reg_cache::name, reg_cache::next, NULL, arm_reg::num, reg_cache::num_regs, number, reg::number, arm::pc, reg::reg_data_type, reg_cache::reg_list, REG_TYPE_CODE_PTR, REG_TYPE_DATA_PTR, REG_TYPE_UINT32, reg::size, target, arm_reg::target, reg_data_type::type, reg::type, arm_reg::value, and reg::value.

Referenced by arm7tdmi_build_reg_cache(), arm9tdmi_build_reg_cache(), arm_dpm_setup(), and xscale_build_reg_cache().

◆ arm_checksum_memory()

| int arm_checksum_memory | ( | struct target * | target, |

| target_addr_t | address, | ||

| uint32_t | count, | ||

| uint32_t * | checksum | ||

| ) |

Runs ARM code in the target to calculate a CRC32 checksum.

Definition at line 1522 of file armv4_5.c.

References working_area::address, arm::arch, ARM_ARCH_V4, ARM_COMMON_MAGIC, ARM_MODE_SVC, ARM_STATE_ARM, ARRAY_SIZE, buf_get_u32(), buf_set_u32(), arm_algorithm::common_magic, arm_algorithm::core_mode, arm_algorithm::core_state, count, destroy_reg_param(), ERROR_OK, init_reg_param(), le_to_h_u32(), LOG_ERROR, NULL, PARAM_IN_OUT, PARAM_OUT, target_alloc_working_area(), target_free_working_area(), target_run_algorithm(), target_to_arm(), target_write_u32(), and reg_param::value.

◆ arm_free_reg_cache()

| void arm_free_reg_cache | ( | struct arm * | arm | ) |

Definition at line 761 of file armv4_5.c.

References reg::arch_info, arm::core_cache, reg::feature, NULL, reg_cache::num_regs, reg::reg_data_type, and reg_cache::reg_list.

Referenced by arm11_dpm_deinit(), arm7tdmi_free_reg_cache(), arm920t_deinit_target(), arm926ejs_deinit_target(), arm946e_deinit_target(), arm966e_deinit_target(), arm9tdmi_deinit_target(), arm_dpm_setup(), cortex_a_deinit_target(), fa526_deinit_target(), and xscale_free_reg_cache().

◆ arm_get_gdb_arch()

◆ arm_get_gdb_reg_list()

| int arm_get_gdb_reg_list | ( | struct target * | target, |

| struct reg ** | reg_list[], | ||

| int * | reg_list_size, | ||

| enum target_register_class | reg_class | ||

| ) |

Definition at line 1194 of file armv4_5.c.

References arm_core_regs, ARM_CORE_TYPE_SEC_EXT, ARM_CORE_TYPE_VIRT_EXT, arm_gdb_dummy_fp_reg, arm_gdb_dummy_fps_reg, ARM_MODE_HYP, ARM_MODE_MON, arm_reg_current(), ARM_VFP_V3, arm::arm_vfp_version, ARRAY_SIZE, arm::core_cache, arm::core_mode, arm::core_type, arm::cpsr, ERROR_FAIL, ERROR_OK, is_arm_mode(), LOG_ERROR, mode, reg::number, REG_CLASS_ALL, REG_CLASS_GENERAL, reg_cache::reg_list, reg::size, and target_to_arm().

◆ arm_init_arch_info()

Definition at line 1705 of file armv4_5.c.

References target::arch_info, ARM_COMMON_MAGIC, ARM_CORE_TYPE_M_PROFILE, ARM_CORE_TYPE_STD, arm_default_mcr(), arm_default_mrc(), arm_full_context(), ARM_MODE_USR, arm_set_cpsr(), arm::common_magic, arm::core_type, ERROR_OK, arm::full_context, arm::mcr, arm::mrc, arm::read_core_reg, target, and arm::target.

Referenced by arm11_target_create(), armv7m_init_arch_info(), and xscale_init_arch_info().

◆ arm_mode_name()

| const char* arm_mode_name | ( | unsigned | psr_mode | ) |

Map PSR mode bits to the name of an ARM processor operating mode.

Definition at line 171 of file armv4_5.c.

References arm_mode_data, ARRAY_SIZE, LOG_ERROR, and psr.

Referenced by adapter_debug_entry(), arm7_9_debug_entry(), arm7_9_restore_context(), arm_arch_state(), arm_set_cpsr(), armv7m_arch_state(), cortex_m_debug_entry(), and xscale_debug_entry().

◆ arm_reg_current()

Returns handle to the register currently mapped to a given number.

Someone must have called arm_set_cpsr() before.

- Parameters

-

arm This core's state and registers are used. regnum From 0..15 corresponding to R0..R14 and PC. Note that R0..R7 don't require mapping; you may access those as the first eight entries in the register cache. Likewise R15 (PC) doesn't need mapping; you may also access it directly. However, R8..R14, and SPSR (arm->spsr) must be mapped. CPSR (arm->cpsr) is also not mapped.

Definition at line 502 of file armv4_5.c.

References arm::core_cache, LOG_ERROR, arm::map, NULL, and reg_cache::reg_list.

Referenced by arm7_9_debug_entry(), arm7_9_read_memory(), arm7_9_soft_reset_halt(), arm7_9_write_memory(), arm_dpm_read_current_registers(), arm_get_gdb_reg_list(), arm_semihosting(), COMMAND_HANDLER(), cortex_a_read_cpu_memory(), cortex_a_read_cpu_memory_slow(), cortex_a_write_cpu_memory(), cortex_a_write_cpu_memory_slow(), post_result(), and xscale_debug_entry().

◆ arm_set_cpsr()

| void arm_set_cpsr | ( | struct arm * | arm, |

| uint32_t | cpsr | ||

| ) |

Configures host-side ARM records to reflect the specified CPSR.

Later, code can use arm_reg_current() to map register numbers according to how they are exposed by this mode.

Definition at line 438 of file armv4_5.c.

References arm_mode_name(), ARM_MODE_SYS, arm_mode_to_number(), ARM_MODE_USR, ARM_STATE_ARM, ARM_STATE_JAZELLE, arm_state_strings, ARM_STATE_THUMB, ARM_STATE_THUMB_EE, armv4_5_core_reg_map, buf_set_u32(), arm::core_cache, arm::core_mode, arm::core_state, arm::cpsr, reg::dirty, LOG_DEBUG, LOG_ERROR, LOG_WARNING, arm::map, mode, NULL, reg_cache::reg_list, arm::spsr, state, reg::valid, and reg::value.

Referenced by arm720t_soft_reset_halt(), arm7_9_debug_entry(), arm7_9_soft_reset_halt(), arm920t_soft_reset_halt(), arm926ejs_soft_reset_halt(), arm_dpm_read_current_registers(), arm_init_arch_info(), armv4_5_run_algorithm_inner(), and xscale_debug_entry().

◆ armv4_5_run_algorithm()

| int armv4_5_run_algorithm | ( | struct target * | target, |

| int | num_mem_params, | ||

| struct mem_param * | mem_params, | ||

| int | num_reg_params, | ||

| struct reg_param * | reg_params, | ||

| target_addr_t | entry_point, | ||

| target_addr_t | exit_point, | ||

| int | timeout_ms, | ||

| void * | arch_info | ||

| ) |

Definition at line 1496 of file armv4_5.c.

References reg::arch_info, armv4_5_run_algorithm_completion(), and armv4_5_run_algorithm_inner().

◆ armv4_5_run_algorithm_inner()

| int armv4_5_run_algorithm_inner | ( | struct target * | target, |

| int | num_mem_params, | ||

| struct mem_param * | mem_params, | ||

| int | num_reg_params, | ||

| struct reg_param * | reg_params, | ||

| uint32_t | entry_point, | ||

| uint32_t | exit_point, | ||

| int | timeout_ms, | ||

| void * | arch_info, | ||

| int(*)(struct target *target, uint32_t exit_point, int timeout_ms, void *arch_info) | run_it | ||

| ) |

Definition at line 1311 of file armv4_5.c.

References arm::arch, reg::arch_info, ARM_ARCH_V4, ARM_COMMON_MAGIC, ARM_MODE_ANY, arm_set_cpsr(), ARM_STATE_ARM, ARM_STATE_THUMB, ARMV4_5_CORE_REG_MODE, armv4_5_set_core_reg(), BKPT_HARD, breakpoint_add(), breakpoint_remove(), buf_get_u32(), buf_set_u32(), arm_algorithm::common_magic, arm::core_cache, arm::core_mode, arm_algorithm::core_mode, arm::core_state, arm_algorithm::core_state, arm::cpsr, direction, reg::dirty, ERROR_COMMAND_SYNTAX_ERROR, ERROR_FAIL, ERROR_OK, ERROR_TARGET_FAILURE, ERROR_TARGET_INVALID, ERROR_TARGET_NOT_HALTED, is_arm_mode(), LOG_DEBUG, LOG_ERROR, LOG_WARNING, PARAM_IN, PARAM_OUT, arm::read_core_reg, reg_param::reg_name, register_get_by_name(), size, reg_param::size, reg::size, target::state, TARGET_HALTED, target_read_buffer(), target_resume(), target_to_arm(), target_write_buffer(), reg::valid, and reg::value.

Referenced by arm7_9_bulk_write_memory(), and armv4_5_run_algorithm().

◆ armv8_build_reg_cache()

Builds cache of architecturally defined registers.

Definition at line 1600 of file armv8.c.

References reg::arch_info, arm_reg::arm, armv8_common::arm, ARMV8_NUM_REGS, ARMV8_NUM_REGS32, ARMV8_PC, armv8_reg32_type, armv8_reg_type, armv8_regs, armv8_regs32, ARMV8_XPSR, reg::caller_save, arm::core_cache, arm::cpsr, data_type, reg::exist, feature, reg::feature, reg::group, LOG_ERROR, arm_reg::mode, reg::name, reg_cache::name, reg_cache::next, NULL, arm_reg::num, reg_cache::num_regs, reg::number, arm::pc, target::reg_cache, reg::reg_data_type, reg_cache::reg_list, register_get_last_cache_p(), reg::size, target, arm_reg::target, target_to_armv8(), reg_data_type::type, reg::type, arm_reg::value, and reg::value.

Referenced by armv8_dpm_setup().

◆ armv8_get_gdb_arch()

| const char* armv8_get_gdb_arch | ( | struct target * | target | ) |

Definition at line 1751 of file armv8.c.

References ARM_STATE_AARCH64, arm::core_state, and target_to_arm().

◆ armv8_get_gdb_reg_list()

| int armv8_get_gdb_reg_list | ( | struct target * | target, |

| struct reg ** | reg_list[], | ||

| int * | reg_list_size, | ||

| enum target_register_class | reg_class | ||

| ) |

Definition at line 1757 of file armv8.c.

References ARM_STATE_AARCH64, ARMV8_LAST_REG, ARMV8_R14, armv8_reg_current(), ARMV8_V0, arm::core_cache, arm::core_state, ERROR_FAIL, ERROR_OK, LOG_DEBUG, LOG_ERROR, reg_cache::next, reg_cache::num_regs, REG_CLASS_ALL, REG_CLASS_GENERAL, reg_cache::reg_list, target_name(), and target_to_arm().

◆ armv8_reg_current()

Definition at line 1694 of file armv8.c.

References ARMV8_LAST_REG, arm::core_cache, NULL, and reg_cache::reg_list.

Referenced by aarch64_read_cpu_memory(), aarch64_read_cpu_memory_fast(), aarch64_read_cpu_memory_slow(), aarch64_write_cpu_memory(), aarch64_write_cpu_memory_fast(), aarch64_write_cpu_memory_slow(), armv8_dpm_read_current_registers(), armv8_dpm_setup(), and armv8_get_gdb_reg_list().

◆ is_arm()

|

inlinestatic |

Definition at line 249 of file arm.h.

References ARM_COMMON_MAGIC, and arm::common_magic.

Referenced by cfi_intel_write_block(), cfi_spansion_write_block(), COMMAND_HANDLER(), stm32x_write_block(), and target_to_armv7m_safe().

◆ is_arm_mode()

| bool is_arm_mode | ( | unsigned | psr_mode | ) |

Return true iff the parameter denotes a valid ARM processor mode.

Definition at line 182 of file armv4_5.c.

References arm_mode_data, ARRAY_SIZE, and psr.

Referenced by arm7_9_debug_entry(), arm7_9_full_context(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm920t_read_cp15_interpreted(), arm920t_write_cp15_interpreted(), arm_get_gdb_reg_list(), armv4_5_run_algorithm_inner(), COMMAND_HANDLER(), and xscale_debug_entry().

◆ target_to_arm()

Convert target handle to generic ARM target state handle.

Definition at line 243 of file arm.h.

References target::arch_info.

Referenced by arm7tdmi_build_reg_cache(), arm7tdmi_free_reg_cache(), arm920t_deinit_target(), arm920t_read_cp15_interpreted(), arm920t_write_cp15_interpreted(), arm926ejs_deinit_target(), arm946e_deinit_target(), arm966e_deinit_target(), arm9tdmi_build_reg_cache(), arm9tdmi_deinit_target(), arm_arch_state(), arm_blank_check_memory(), arm_checksum_memory(), arm_dpm_full_context(), arm_dpm_read_core_reg(), arm_dpm_write_core_reg(), arm_full_context(), arm_get_gdb_reg_list(), arm_semihosting(), arm_semihosting_init(), arm_simulate_step(), armv4_5_run_algorithm_completion(), armv4_5_run_algorithm_inner(), armv7m_get_core_reg(), armv8_aarch64_state(), armv8_dpm_full_context(), armv8_dpm_read_core_reg(), armv8_dpm_write_core_reg(), armv8_get_core_reg(), armv8_get_core_reg32(), armv8_get_gdb_arch(), armv8_get_gdb_reg_list(), armv8_mmu_translate_va_pa(), cfi_intel_write_block(), cfi_spansion_write_block(), COMMAND_HANDLER(), dpm_add_breakpoint(), dpm_add_watchpoint(), dpm_mcr(), dpm_mrc(), dpm_remove_breakpoint(), dpm_remove_watchpoint(), dpmv8_add_breakpoint(), dpmv8_add_watchpoint(), dpmv8_mcr(), dpmv8_mrc(), dpmv8_remove_breakpoint(), dpmv8_remove_watchpoint(), etm_setup(), fa526_deinit_target(), post_result(), stm32x_write_block(), target_to_armv7m_safe(), xscale_full_context(), xscale_restore_banked(), and xscale_step().

Variable Documentation

◆ arm_all_profiles_command_handlers

|

extern |

◆ arm_command_handlers

|

extern |