Data Fields | |

| void * | arch_info |

| bool | caller_save |

| bool | dirty |

| bool | exist |

| struct reg_feature * | feature |

| const char * | group |

| bool | hidden |

| const char * | name |

| uint32_t | number |

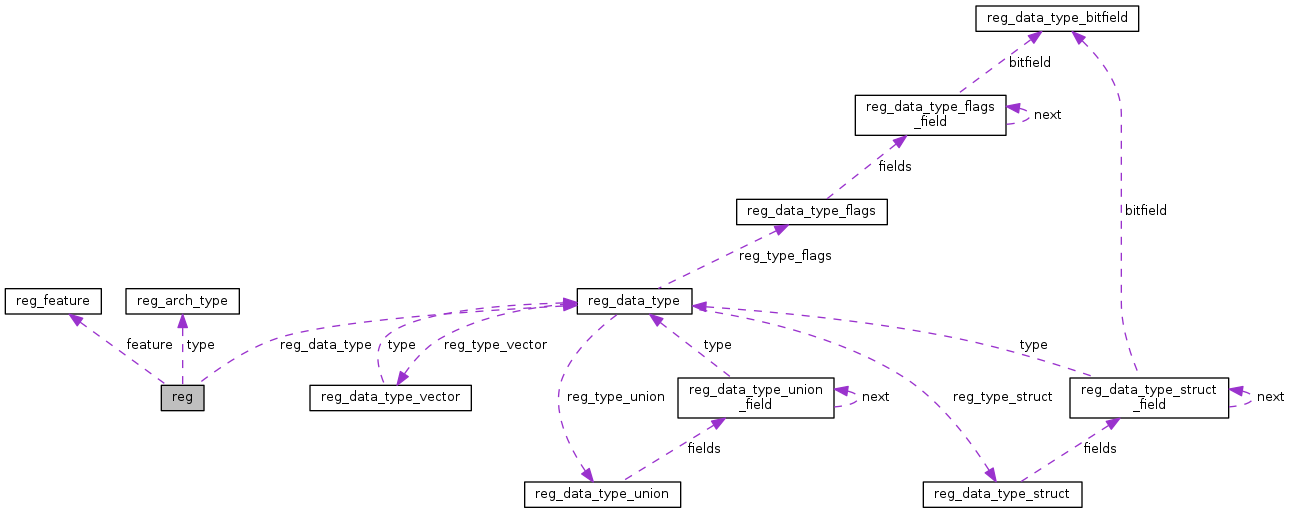

| struct reg_data_type * | reg_data_type |

| uint32_t | size |

| const struct reg_arch_type * | type |

| bool | valid |

| uint8_t * | value |

Detailed Description

Definition at line 111 of file register.h.

Field Documentation

◆ arch_info

| void* reg::arch_info |

Definition at line 140 of file register.h.

Referenced by access_register_command(), arc_get_register(), arc_init_reg(), arc_restore_context(), arc_save_context(), arm7_9_dcc_completion(), arm7_9_read_core_reg(), arm7_9_restore_context(), arm7_9_write_core_reg(), arm_build_reg_cache(), arm_dpm_full_context(), arm_dpm_write_dirty_registers(), arm_free_reg_cache(), armv4_5_get_core_reg(), armv4_5_run_algorithm(), armv4_5_run_algorithm_inner(), armv7m_build_reg_cache(), armv7m_free_reg_cache(), armv7m_get_core_reg(), armv7m_read_core_reg(), armv7m_set_core_reg(), armv7m_write_core_reg(), armv8_build_reg_cache(), armv8_dpm_full_context(), armv8_dpm_write_dirty_registers(), armv8_free_cache(), armv8_get_core_reg(), armv8_get_core_reg32(), avr32_build_reg_cache(), avr32_get_core_reg(), cortex_m_dwt_addreg(), cortex_m_dwt_free(), cortex_m_dwt_get_reg(), cortex_m_dwt_set_reg(), dsp563xx_build_reg_cache(), dsp563xx_debug_init(), dsp563xx_get_core_reg(), dsp563xx_invalidate_x_context(), dsp563xx_read_register(), dsp563xx_reg_ssh_read(), dsp563xx_reg_ssh_write(), dsp563xx_reg_ssl_read(), dsp563xx_write_register(), embeddedice_build_reg_cache(), embeddedice_free_reg_cache(), embeddedice_read_reg_w_check(), embeddedice_write_reg(), esirisc_build_reg_cache(), esirisc_get_reg(), esirisc_read_csr(), esirisc_read_reg(), esirisc_restore_context(), esirisc_save_context(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etb_read_reg_w_check(), etb_write_reg(), etm_read_reg_w_check(), etm_reg_add(), etm_reg_lookup(), etm_write_reg(), lakemont_build_reg_cache(), lakemont_get_core_reg(), mips32_build_reg_cache(), mips32_get_core_reg(), mips32_set_core_reg(), mips64_build_reg_cache(), mips64_get_core_reg(), mips64_set_core_reg(), nds32_build_reg_cache(), nds32_get_all_reg_list(), nds32_get_core_reg(), nds32_get_core_reg_64(), nds32_get_general_reg_list(), nds32_init_must_have_registers(), nds32_init_option_registers(), nds32_restore_context(), nds32_set_core_reg(), or1k_build_reg_cache(), or1k_get_core_reg(), read_hw_reg(), register_get(), register_set(), riscv_free_registers(), riscv_init_registers(), stm8_build_reg_cache(), stm8_free_reg_cache(), stm8_get_core_reg(), stm8_set_core_reg(), write_hw_reg(), xscale_free_reg_cache(), xscale_get_reg(), xscale_set_reg(), xscale_write_dcsr_sw(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), and xtensa_core_reg_get().

◆ caller_save

| bool reg::caller_save |

Definition at line 119 of file register.h.

Referenced by arc_init_reg(), arm_build_reg_cache(), armv7m_build_reg_cache(), armv8_build_reg_cache(), gdb_generate_target_description(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), riscv_init_registers(), and stm8_build_reg_cache().

◆ dirty

| bool reg::dirty |

Definition at line 124 of file register.h.

Referenced by aarch64_read_cpu_memory(), aarch64_read_cpu_memory_fast(), aarch64_read_cpu_memory_slow(), aarch64_restore_one(), aarch64_write_cpu_memory(), aarch64_write_cpu_memory_fast(), aarch64_write_cpu_memory_slow(), adapter_resume(), adapter_step(), arc_get_register(), arc_restore_context(), arc_resume(), arc_save_context(), arc_step(), arm11_nextpc(), arm11_read_memory_inner(), arm11_write_memory_inner(), arm720t_soft_reset_halt(), arm7_9_debug_entry(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_soft_reset_halt(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm920t_read_cp15_interpreted(), arm920t_soft_reset_halt(), arm920t_write_cp15_interpreted(), arm926ejs_soft_reset_halt(), arm_dpm_read_current_registers(), arm_dpm_read_reg(), arm_dpm_write_dirty_registers(), arm_set_cpsr(), armv4_5_get_core_reg(), armv4_5_run_algorithm_inner(), armv7m_build_reg_cache(), armv7m_read_core_reg(), armv7m_restore_context(), armv7m_set_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_dpm_handle_exception(), armv8_dpm_modeswitch(), armv8_dpm_write_dirty_registers(), armv8_read_reg_simdfp_aarch32(), armv8_set_cpsr(), armv8_write_reg_simdfp_aarch32(), avr32_ap7k_restore_context(), avr32_build_reg_cache(), avr32_read_core_reg(), avr32_write_core_reg(), COMMAND_HANDLER(), cortex_a_internal_restore(), cortex_a_read_cpu_memory(), cortex_a_read_cpu_memory_slow(), cortex_a_write_cpu_memory(), cortex_a_write_cpu_memory_slow(), cortex_m_fast_read_all_regs(), cortex_m_resume(), cortex_m_step(), dpm_read_reg_u64(), dpm_write_reg(), dpm_write_reg_u64(), dpmv8_read_reg(), dpmv8_write_reg(), dsp563xx_build_reg_cache(), dsp563xx_debug_init(), dsp563xx_invalidate_x_context(), dsp563xx_read_core_reg(), dsp563xx_read_memory_core(), dsp563xx_reg_pc_read(), dsp563xx_reg_read_high_io(), dsp563xx_reg_write_high_io(), dsp563xx_resume(), dsp563xx_step_ex(), dsp563xx_write_core_reg(), dsp563xx_write_memory_core(), dsp563xx_write_register(), embeddedice_build_reg_cache(), embeddedice_set_reg(), esirisc_read_csr(), esirisc_read_reg(), esirisc_restore_context(), esirisc_resume_or_step(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etb_set_reg(), etm_set_reg(), feroceon_bulk_write_memory(), lakemont_build_reg_cache(), lakemont_poll(), mips32_build_reg_cache(), mips32_read_core_reg(), mips32_restore_context(), mips32_run_algorithm(), mips32_set_core_reg(), mips32_write_core_reg(), mips64_invalidate_core_regs(), mips64_read_core_reg(), mips64_restore_context(), mips64_set_core_reg(), mips64_write_core_reg(), mips_m4k_internal_restore(), mips_m4k_step(), mips_mips64_resume(), mips_mips64_step(), nds32_get_core_reg(), nds32_get_core_reg_64(), nds32_restore_context(), nds32_set_core_reg(), or1k_build_reg_cache(), or1k_read_core_reg(), or1k_restore_context(), or1k_write_core_reg(), post_result(), read_hw_reg(), register_cache_invalidate(), restore_context(), riscv_init_registers(), set_debug_regs(), stm8_build_reg_cache(), stm8_read_core_reg(), stm8_restore_context(), stm8_resume(), stm8_run_algorithm(), stm8_set_core_reg(), stm8_step(), stm8_write_core_reg(), unset_debug_regs(), write_hw_reg(), xscale_debug_entry(), xscale_full_context(), xscale_get_reg(), xscale_read_dcsr(), xscale_restore_banked(), xscale_write_dcsr(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), xtensa_cause_clear(), xtensa_fetch_all_regs(), xtensa_mark_register_dirty(), xtensa_reg_set_value(), and xtensa_write_dirty_registers().

◆ exist

| bool reg::exist |

Definition at line 128 of file register.h.

Referenced by adapter_load_context(), arc_build_bcr_reg_cache(), arc_get_gdb_reg_list(), arc_restore_context(), arc_save_context(), arm_build_reg_cache(), arm_dpm_full_context(), arm_dpm_write_dirty_registers(), arm_full_context(), armv7m_build_reg_cache(), armv7m_restore_context(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv8_build_reg_cache(), armv8_dpm_full_context(), armv8_dpm_write_dirty_registers(), COMMAND_HANDLER(), cortex_m_examine(), cortex_m_fast_read_all_regs(), cortex_m_slow_read_all_regs(), dsp563xx_build_reg_cache(), esirisc_build_reg_cache(), esirisc_restore_context(), esirisc_save_context(), gdb_generate_target_description(), gdb_get_register_packet(), gdb_get_registers_packet(), gdb_set_register_packet(), gdb_set_registers_packet(), hwthread_get_thread_reg_list(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_get_all_reg_list(), or1k_build_reg_cache(), register_cache_invalidate(), register_get_by_name(), register_get_by_number(), riscv_get_gdb_reg_list_internal(), riscv_get_register(), riscv_init_registers(), smp_reg_list_noread(), stm8_build_reg_cache(), target_jim_get_reg(), target_jim_set_reg(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), xtensa_core_reg_get(), and xtensa_get_gdb_reg_list().

◆ feature

| struct reg_feature* reg::feature |

Definition at line 117 of file register.h.

Referenced by arc_init_reg(), arm_build_reg_cache(), arm_free_reg_cache(), armv7m_build_reg_cache(), armv7m_free_reg_cache(), armv8_build_reg_cache(), armv8_free_cache(), get_reg_features_list(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), or1k_build_reg_cache(), riscv_init_registers(), stm8_build_reg_cache(), and stm8_free_reg_cache().

◆ group

| const char* reg::group |

Definition at line 138 of file register.h.

Referenced by arc_init_reg(), arm_build_reg_cache(), armv7m_build_reg_cache(), armv8_build_reg_cache(), esirisc_build_reg_cache(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), or1k_build_reg_cache(), riscv_init_registers(), and stm8_build_reg_cache().

◆ hidden

| bool reg::hidden |

Definition at line 130 of file register.h.

Referenced by armv7m_build_reg_cache(), COMMAND_HANDLER(), gdb_generate_target_description(), gdb_get_register_packet(), gdb_get_registers_packet(), gdb_set_register_packet(), gdb_set_registers_packet(), and hwthread_get_thread_reg_list().

◆ name

| const char* reg::name |

Definition at line 113 of file register.h.

Referenced by arc_init_reg(), arc_reg_get_by_name(), arm7_9_restore_context(), arm_build_reg_cache(), arm_dpm_read_reg(), armv7m_build_reg_cache(), armv7m_read_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_build_reg_cache(), avr32_build_reg_cache(), COMMAND_HANDLER(), cortex_m_dwt_addreg(), dpm_read_reg_u64(), dpm_write_reg(), dpm_write_reg_u64(), dpmv8_read_reg(), dpmv8_write_reg(), dsp563xx_build_reg_cache(), embeddedice_build_reg_cache(), esirisc_build_reg_cache(), esirisc_read_csr(), esirisc_read_reg(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etm_reg_add(), jim_arc_add_reg(), lakemont_build_reg_cache(), lakemont_get_core_reg(), mips32_build_reg_cache(), mips32_run_algorithm(), mips64_build_reg_cache(), nds32_build_reg_cache(), nds32_get_core_reg(), nds32_restore_context(), nds32_set_core_reg(), or1k_build_reg_cache(), read_all_core_hw_regs(), read_hw_reg(), read_hw_reg_to_cache(), reg_cache_get(), reg_cache_set(), register_get(), register_get_by_name(), register_set(), riscv_init_registers(), riscv_run_algorithm(), riscv_set_register(), sam3_get_info(), sam3_get_reg(), sam3_read_all_regs(), sam3_read_this_reg(), sam4_get_info(), sam4_get_reg(), sam4_read_all_regs(), sam4_read_this_reg(), smp_reg_list_noread(), stm8_build_reg_cache(), stm8_run_algorithm(), validate_register(), write_all_core_hw_regs(), write_hw_reg(), write_hw_reg_from_cache(), x86_32_get_gdb_reg_list(), xscale_get_reg(), xscale_set_reg(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), xtensa_core_reg_get(), xtensa_do_step(), and xtensa_free_reg_cache().

◆ number

| uint32_t reg::number |

Definition at line 115 of file register.h.

Referenced by arc_get_register(), arc_init_reg(), arm_build_reg_cache(), arm_get_gdb_reg_list(), armv7m_build_reg_cache(), armv7m_get_core_reg(), armv7m_read_core_reg(), armv7m_write_core_reg(), armv8_build_reg_cache(), esirisc_build_reg_cache(), esirisc_read_reg(), esirisc_write_reg(), hwthread_get_thread_reg(), hwthread_get_thread_reg_list(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), or1k_build_reg_cache(), register_get(), register_get_by_number(), register_set(), riscv_init_registers(), riscv_run_algorithm(), stm8_build_reg_cache(), and xtensa_build_reg_cache().

◆ reg_data_type

| struct reg_data_type* reg::reg_data_type |

Definition at line 135 of file register.h.

Referenced by arc_init_reg(), arc_reg_get_field(), arm_build_reg_cache(), arm_free_reg_cache(), armv7m_build_reg_cache(), armv7m_free_reg_cache(), armv8_build_reg_cache(), armv8_free_cache(), esirisc_build_reg_cache(), gdb_generate_target_description(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), riscv_init_registers(), stm8_build_reg_cache(), and stm8_free_reg_cache().

◆ size

| uint32_t reg::size |

Definition at line 132 of file register.h.

Referenced by arc_init_reg(), arm7_9_execute_sys_speed(), arm7_9_resume(), arm_build_reg_cache(), arm_get_gdb_reg_list(), armv4_5_run_algorithm_inner(), armv7m_build_reg_cache(), armv7m_read_core_reg(), armv7m_set_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_build_reg_cache(), avr32_build_reg_cache(), COMMAND_HANDLER(), cortex_m_dwt_addreg(), cortex_m_dwt_set_reg(), cortex_m_fast_read_all_regs(), dpmv8_read_reg(), dpmv8_write_reg(), dsp563xx_build_reg_cache(), dsp563xx_run_algorithm(), embeddedice_build_reg_cache(), embeddedice_set_reg(), embeddedice_set_reg_w_exec(), embeddedice_store_reg(), esirisc_arch_state(), esirisc_build_reg_cache(), esirisc_debug_entry(), esirisc_read_csr(), esirisc_read_reg(), esirisc_resume_or_step(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etb_set_reg(), etb_set_reg_w_exec(), etm_reg_add(), etm_set_reg(), etm_set_reg_w_exec(), etm_store_reg(), gdb_str_to_target(), hwthread_get_thread_reg(), hwthread_get_thread_reg_list(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips32_run_algorithm(), mips64_build_reg_cache(), nds32_build_reg_cache(), or1k_build_reg_cache(), reg_cache_get(), reg_cache_set(), register_get(), register_read(), register_set(), register_size(), register_write_direct(), riscv_get_gdb_reg_list_internal(), riscv_get_register(), riscv_init_registers(), riscv_run_algorithm(), riscv_set_register(), smp_reg_list_noread(), stm8_build_reg_cache(), stm8_set_core_reg(), target_jim_get_reg(), target_jim_set_reg(), xtensa_build_reg_cache(), and xtensa_canonical_to_windowbase_offset().

◆ type

| const struct reg_arch_type* reg::type |

Definition at line 141 of file register.h.

Referenced by arc_get_register_value(), arc_init_reg(), arc_reg_get_field(), arc_set_register_value(), arm_build_reg_cache(), armv7m_build_reg_cache(), armv8_build_reg_cache(), avr32_build_reg_cache(), COMMAND_HANDLER(), cortex_m_dwt_addreg(), dsp563xx_build_reg_cache(), embeddedice_build_reg_cache(), esirisc_build_reg_cache(), etb_build_reg_cache(), etm_reg_add(), gdb_get_register_packet(), gdb_get_registers_packet(), gdb_set_register_packet(), gdb_set_registers_packet(), get_current(), hwthread_get_thread_reg(), hwthread_get_thread_reg_list(), hwthread_set_reg(), lakemont_build_reg_cache(), mips32_build_reg_cache(), mips64_build_reg_cache(), nds32_build_reg_cache(), nds32_get_mapped_reg(), nds32_set_mapped_reg(), or1k_build_reg_cache(), register_init_dummy(), riscv_get_gdb_reg_list_internal(), riscv_init_registers(), riscv_run_algorithm(), stm8_build_reg_cache(), target_jim_get_reg(), target_jim_set_reg(), and xtensa_build_reg_cache().

◆ valid

| bool reg::valid |

Definition at line 126 of file register.h.

Referenced by aarch64_restore_one(), adapter_load_context(), adapter_resume(), adapter_step(), arc_get_register(), arc_get_register_value(), arc_reg_get_field(), arc_restore_context(), arc_resume(), arc_save_context(), arc_step(), arm11_nextpc(), arm720t_soft_reset_halt(), arm7_9_debug_entry(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_setup_semihosting(), arm7_9_soft_reset_halt(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm920t_soft_reset_halt(), arm926ejs_soft_reset_halt(), arm_dpm_full_context(), arm_dpm_read_current_registers(), arm_dpm_read_reg(), arm_full_context(), arm_semihosting(), arm_set_cpsr(), armv4_5_get_core_reg(), armv4_5_run_algorithm_inner(), armv7m_build_reg_cache(), armv7m_read_core_reg(), armv7m_set_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_dpm_full_context(), armv8_dpm_write_dirty_registers(), armv8_get_core_reg32(), armv8_set_cpsr(), avr32_ap7k_save_context(), avr32_build_reg_cache(), avr32_read_core_reg(), avr32_write_core_reg(), COMMAND_HANDLER(), cortex_a_internal_restore(), cortex_m_fast_read_all_regs(), cortex_m_resume(), cortex_m_step(), dpm_read_reg_u64(), dpmv8_read_reg(), dsp563xx_build_reg_cache(), dsp563xx_invalidate_x_context(), dsp563xx_read_core_reg(), dsp563xx_read_memory_core(), dsp563xx_read_register(), dsp563xx_reg_read_high_io(), dsp563xx_reg_write_high_io(), dsp563xx_write_core_reg(), dsp563xx_write_memory_core(), dsp563xx_write_register(), embeddedice_build_reg_cache(), embeddedice_set_reg(), esirisc_read_csr(), esirisc_read_reg(), esirisc_resume_or_step(), esirisc_save_context(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etb_set_reg(), etm_set_reg(), execute_resume(), feroceon_bulk_write_memory(), gdb_get_register_packet(), gdb_get_registers_packet(), get_current(), get_register(), hwthread_get_thread_reg_list(), lakemont_build_reg_cache(), lakemont_poll(), mips32_build_reg_cache(), mips32_read_core_reg(), mips32_run_algorithm(), mips32_save_context(), mips32_set_core_reg(), mips32_write_core_reg(), mips64_invalidate_core_regs(), mips64_read_core_reg(), mips64_set_core_reg(), mips64_write_core_reg(), mips_m4k_internal_restore(), mips_m4k_step(), mips_mips64_resume(), mips_mips64_step(), nds32_get_core_reg(), nds32_get_core_reg_64(), nds32_restore_context(), nds32_set_core_reg(), or1k_build_reg_cache(), or1k_read_core_reg(), or1k_save_context(), or1k_write_core_reg(), read_hw_reg(), reg_cache_get(), reg_cache_set(), register_cache_invalidate(), register_get(), register_set(), restore_context(), riscv_get_gdb_reg_list_internal(), riscv_get_register(), riscv_init_registers(), riscv_invalidate_register_cache(), riscv_set_register(), set_debug_regs(), stm8_build_reg_cache(), stm8_read_core_reg(), stm8_resume(), stm8_run_algorithm(), stm8_save_context(), stm8_set_core_reg(), stm8_step(), stm8_write_core_reg(), unset_debug_regs(), update_mstatus_actual(), write_hw_reg(), xscale_debug_entry(), xscale_full_context(), xscale_get_reg(), xscale_read_dcsr(), xscale_write_dcsr(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), and xtensa_fetch_all_regs().

◆ value

| uint8_t* reg::value |

Definition at line 122 of file register.h.

Referenced by aarch64_restore_one(), adapter_debug_entry(), adapter_poll(), adapter_resume(), adapter_step(), arc_get_register(), arc_get_register_value(), arc_icache_invalidate(), arc_init_reg(), arc_reg_get_field(), arc_restore_context(), arc_resume(), arc_save_context(), arc_set_register_value(), arc_step(), arm11_nextpc(), arm720t_soft_reset_halt(), arm7_9_clear_halt(), arm7_9_debug_entry(), arm7_9_enable_eice_step(), arm7_9_execute_sys_speed(), arm7_9_full_context(), arm7_9_halt(), arm7_9_handle_target_request(), arm7_9_poll(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_resume(), arm7_9_setup_semihosting(), arm7_9_soft_reset_halt(), arm7_9_step(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm7tdmi_branch_resume_thumb(), arm920t_read_cp15_interpreted(), arm920t_soft_reset_halt(), arm920t_write_cp15_interpreted(), arm926ejs_examine_debug_reason(), arm926ejs_soft_reset_halt(), arm9tdmi_branch_resume_thumb(), arm9tdmi_disable_single_step(), arm9tdmi_enable_single_step(), arm_arch_state(), arm_build_reg_cache(), arm_dpm_modeswitch(), arm_dpm_read_reg(), arm_semihosting(), arm_set_cpsr(), armv4_5_get_cpsr(), armv4_5_get_reg(), armv4_5_run_algorithm_completion(), armv4_5_run_algorithm_inner(), armv4_5_set_reg(), armv7m_arch_state(), armv7m_build_reg_cache(), armv7m_read_core_reg(), armv7m_restore_context(), armv7m_set_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_aarch64_state(), armv8_build_reg_cache(), armv8_dpm_modeswitch(), armv8_set_cpsr(), avr32_ap7k_resume(), avr32_build_reg_cache(), avr32_read_core_reg(), avr32_write_core_reg(), calcaddr_physfromlin(), COMMAND_HANDLER(), cortex_a_internal_restore(), cortex_a_step(), cortex_m_debug_entry(), cortex_m_dwt_addreg(), cortex_m_fast_read_all_regs(), cortex_m_resume(), cortex_m_step(), dpm_read_reg_u64(), dpm_write_pc_core_state(), dpm_write_reg(), dpm_write_reg_u64(), dpmv8_read_reg(), dpmv8_write_reg(), dsp563xx_build_reg_cache(), dsp563xx_read_core_reg(), dsp563xx_run_algorithm(), dsp563xx_write_core_reg(), embeddedice_build_reg_cache(), embeddedice_free_reg_cache(), embeddedice_read_reg_w_check(), embeddedice_set_reg(), embeddedice_setup(), embeddedice_store_reg(), esirisc_arch_state(), esirisc_build_reg_cache(), esirisc_debug_entry(), esirisc_read_csr(), esirisc_read_reg(), esirisc_resume_or_step(), esirisc_write_csr(), esirisc_write_reg(), etb_build_reg_cache(), etb_init(), etb_read_reg_w_check(), etb_read_trace(), etb_set_reg(), etb_status(), etm_read_reg_w_check(), etm_reg_add(), etm_set_reg(), etm_setup(), etm_store_reg(), execute_resume(), feroceon_branch_resume_thumb(), feroceon_bulk_write_memory(), feroceon_set_dbgrq(), gdb_str_to_target(), get_current(), get_register(), halt_prep(), hwthread_get_thread_reg(), hwthread_get_thread_reg_list(), lakemont_arch_state(), lakemont_build_reg_cache(), lakemont_get_core_reg(), lakemont_poll(), lakemont_resume(), lakemont_step(), mips32_arch_state(), mips32_build_reg_cache(), mips32_read_core_reg(), mips32_run_algorithm(), mips32_run_and_wait(), mips32_set_core_reg(), mips32_write_core_reg(), mips64_arch_state(), mips64_build_reg_cache(), mips64_read_core_reg(), mips64_set_core_reg(), mips64_write_core_reg(), mips_m4k_debug_entry(), mips_m4k_internal_restore(), mips_m4k_step(), mips_mips64_debug_entry(), mips_mips64_resume(), mips_mips64_step(), nds32_arch_state(), nds32_build_reg_cache(), nds32_full_context(), nds32_get_mapped_reg(), nds32_restore_context(), nds32_set_core_reg(), nds32_set_mapped_reg(), or1k_build_reg_cache(), or1k_read_core_reg(), or1k_resume_or_step(), or1k_write_core_reg(), post_result(), read_hw_reg(), read_mem(), reg_cache_get(), reg_cache_set(), register_get(), register_read(), register_read_direct(), register_set(), register_write(), register_write_direct(), riscv_free_registers(), riscv_get_register(), riscv_init_registers(), riscv_run_algorithm(), riscv_set_register(), set_debug_regs(), set_register(), stm8_arch_state(), stm8_build_reg_cache(), stm8_debug_entry(), stm8_free_reg_cache(), stm8_read_core_reg(), stm8_resume(), stm8_run_algorithm(), stm8_run_and_wait(), stm8_set_core_reg(), stm8_step(), stm8_write_core_reg(), target_jim_get_reg(), target_profiling_default(), target_read_u16(), target_read_u32(), target_read_u64(), target_read_u8(), target_write_phys_u16(), target_write_phys_u32(), target_write_phys_u64(), target_write_phys_u8(), target_write_u16(), target_write_u32(), target_write_u64(), target_write_u8(), unset_debug_regs(), write_hw_reg(), write_hw_reg_from_cache(), write_mem(), x86_32_common_read_io(), x86_32_common_virt2phys(), x86_32_common_write_io(), x86_32_get_gdb_reg_list(), xscale_assert_reset(), xscale_deassert_reset(), xscale_debug_entry(), xscale_disable_mmu_caches(), xscale_enable_mmu_caches(), xscale_enable_single_step(), xscale_free_reg_cache(), xscale_full_context(), xscale_get_reg(), xscale_get_ttb(), xscale_read_dcsr(), xscale_read_memory(), xscale_read_trace(), xscale_read_tx(), xscale_restore_banked(), xscale_resume(), xscale_send_u32(), xscale_set_reg(), xscale_set_watchpoint(), xscale_step(), xscale_step_inner(), xscale_unset_watchpoint(), xscale_write_dcsr(), xscale_write_dcsr_sw(), xscale_write_memory(), xscale_write_rx(), xtensa_build_reg_cache(), xtensa_canonical_to_windowbase_offset(), xtensa_free_reg_cache(), xtensa_reg_get_value(), xtensa_reg_set(), and xtensa_reg_set_value().

The documentation for this struct was generated from the following file: