This is the interface to the Debug Programmers Model for ARMv6 and ARMv7 processors. More...

Go to the source code of this file.

Data Structures | |

| struct | arm_dpm |

| This wraps an implementation of DPM primitives. More... | |

| struct | dpm_bp |

| struct | dpm_bpwp |

| struct | dpm_wp |

Macros | |

| #define | DRCR_CLEAR_EXCEPTIONS (1 << 2) |

| #define | DRCR_HALT (1 << 0) |

| #define | DRCR_RESTART (1 << 1) |

| #define | DSCR_CORE_HALTED (0x1 << 0) |

| #define | DSCR_CORE_RESTARTED (0x1 << 1) |

| #define | DSCR_CP14_USR_COMMS (0x1 << 12) |

| #define | DSCR_DBG_ACK (0x1 << 10) |

| #define | DSCR_DBG_NOPWRDWN (0x1 << 9) /* v6 only */ |

| #define | DSCR_DSCRD_IMPRECISE_ABORT (0x1 << 19) |

| #define | DSCR_DTR_RX_FULL (0x1 << 30) /* bit 31 is reserved */ |

| #define | DSCR_DTR_TX_FULL (0x1 << 29) |

| #define | DSCR_DTRRX_FULL_LATCHED (0x1 << 27) /* bit 28 is reserved */ |

| #define | DSCR_DTRTX_FULL_LATCHED (0x1 << 26) |

| #define | DSCR_ENTRY(dscr) ((dscr) & 0x3f) |

| #define | DSCR_ENTRY_BKPT_INSTR (0x0F) |

| #define | DSCR_ENTRY_BREAKPOINT (0x07) |

| #define | DSCR_ENTRY_D_SIDE_ABORT (0x1B) /* v6 only */ |

| #define | DSCR_ENTRY_EXT_DBG_REQ (0x13) |

| #define | DSCR_ENTRY_HALT_REQ (0x03) |

| #define | DSCR_ENTRY_I_SIDE_ABORT (0x1F) /* v6 only */ |

| #define | DSCR_ENTRY_IMPRECISE_WATCHPT (0x0B) |

| #define | DSCR_ENTRY_MASK (0xF << 2) |

| #define | DSCR_ENTRY_OS_UNLOCK (0x23) |

| #define | DSCR_ENTRY_PRECISE_WATCHPT (0x2B) |

| #define | DSCR_ENTRY_VECT_CATCH (0x17) |

| #define | DSCR_EXT_DCC_FAST_MODE (0x2 << 20) /* bits 22, 23 are reserved */ |

| #define | DSCR_EXT_DCC_MASK (0x3 << 20) /* DTR mode */ /* bits 22, 23 are reserved */ |

| #define | DSCR_EXT_DCC_NON_BLOCKING (0x0 << 20) |

| #define | DSCR_EXT_DCC_STALL_MODE (0x1 << 20) |

| #define | DSCR_HALT_DBG_MODE (0x1 << 14) |

| #define | DSCR_INSTR_COMP (0x1 << 24) |

| #define | DSCR_INT_DIS (0x1 << 11) |

| #define | DSCR_ITR_EN (0x1 << 13) |

| #define | DSCR_MON_DBG_MODE (0x1 << 15) |

| #define | DSCR_NON_SECURE (0x1 << 18) |

| #define | DSCR_PIPE_ADVANCE (0x1 << 25) |

| #define | DSCR_RUN_MODE(dscr) ((dscr) & 0x03) |

| #define | DSCR_SEC_PRIV_INVASV_DIS (0x1 << 16) |

| #define | DSCR_SEC_PRIV_NINVASV_DIS (0x1 << 17) |

| #define | DSCR_STICKY_ABORT_IMPRECISE (0x1 << 7) |

| #define | DSCR_STICKY_ABORT_PRECISE (0x1 << 6) |

| #define | DSCR_STICKY_UNDEFINED (0x1 << 8) |

| #define | OSLSR_NTT (1 << 2) |

| #define | OSLSR_OSLK (1 << 1) |

| #define | OSLSR_OSLM (OSLSR_OSLM0|OSLSR_OSLM1) |

| #define | OSLSR_OSLM0 (1 << 0) |

| #define | OSLSR_OSLM1 (1 << 3) |

| #define | PRCR_DEBUG_NO_POWER_DOWN (1 << 0) |

| #define | PRCR_HOLD_NON_DEBUG_RESET (1 << 2) |

| #define | PRCR_WARM_RESET (1 << 1) |

| #define | PRSR_DLK (1 << 6) /* v7.1 Debug only */ |

| #define | PRSR_HALTED (1 << 4) /* v7.1 Debug only */ |

| #define | PRSR_OSLK (1 << 5) /* v7.1 Debug only */ |

| #define | PRSR_POWERUP_STATUS (1 << 0) |

| #define | PRSR_RESET_STATUS (1 << 2) |

| #define | PRSR_STICKY_POWERDOWN_STATUS (1 << 1) |

| #define | PRSR_STICKY_RESET_STATUS (1 << 3) |

Functions | |

| int | arm_dpm_initialize (struct arm_dpm *dpm) |

| Reinitializes DPM state at the beginning of a new debug session or after a reset which may have affected the debug module. More... | |

| int | arm_dpm_modeswitch (struct arm_dpm *dpm, enum arm_mode mode) |

| int | arm_dpm_read_current_registers (struct arm_dpm *dpm) |

| Read basic registers of the current context: R0 to R15, and CPSR; sets the core mode (such as USR or IRQ) and state (such as ARM or Thumb). More... | |

| int | arm_dpm_read_reg (struct arm_dpm *dpm, struct reg *r, unsigned regnum) |

| void | arm_dpm_report_dscr (struct arm_dpm *dpm, uint32_t dcsr) |

| void | arm_dpm_report_wfar (struct arm_dpm *dpm, uint32_t wfar) |

| int | arm_dpm_setup (struct arm_dpm *dpm) |

| Hooks up this DPM to its associated target; call only once. More... | |

| int | arm_dpm_write_dirty_registers (struct arm_dpm *dpm, bool bpwp) |

| Writes all modified core registers for all processor modes. More... | |

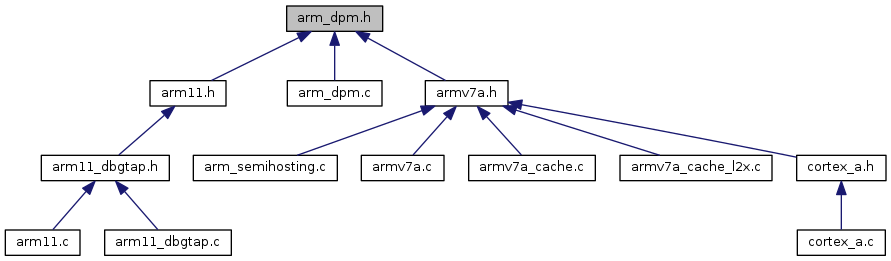

Detailed Description

This is the interface to the Debug Programmers Model for ARMv6 and ARMv7 processors.

ARMv6 processors (such as ARM11xx implementations) introduced a model which became part of the ARMv7-AR architecture which is most familiar through the Cortex-A series parts. While specific details differ (like how to write the instruction register), the high level models easily support shared code because those registers are compatible.

Definition in file arm_dpm.h.

Macro Definition Documentation

◆ DRCR_CLEAR_EXCEPTIONS

◆ DRCR_HALT

◆ DRCR_RESTART

◆ DSCR_CORE_HALTED

◆ DSCR_CORE_RESTARTED

◆ DSCR_CP14_USR_COMMS

◆ DSCR_DBG_ACK

◆ DSCR_DBG_NOPWRDWN

◆ DSCR_DSCRD_IMPRECISE_ABORT

◆ DSCR_DTR_RX_FULL

| #define DSCR_DTR_RX_FULL (0x1 << 30) /* bit 31 is reserved */ |

◆ DSCR_DTR_TX_FULL

◆ DSCR_DTRRX_FULL_LATCHED

| #define DSCR_DTRRX_FULL_LATCHED (0x1 << 27) /* bit 28 is reserved */ |

◆ DSCR_DTRTX_FULL_LATCHED

◆ DSCR_ENTRY

◆ DSCR_ENTRY_BKPT_INSTR

◆ DSCR_ENTRY_BREAKPOINT

◆ DSCR_ENTRY_D_SIDE_ABORT

◆ DSCR_ENTRY_EXT_DBG_REQ

◆ DSCR_ENTRY_HALT_REQ

◆ DSCR_ENTRY_I_SIDE_ABORT

◆ DSCR_ENTRY_IMPRECISE_WATCHPT

◆ DSCR_ENTRY_MASK

◆ DSCR_ENTRY_OS_UNLOCK

◆ DSCR_ENTRY_PRECISE_WATCHPT

◆ DSCR_ENTRY_VECT_CATCH

◆ DSCR_EXT_DCC_FAST_MODE

| #define DSCR_EXT_DCC_FAST_MODE (0x2 << 20) /* bits 22, 23 are reserved */ |

◆ DSCR_EXT_DCC_MASK

◆ DSCR_EXT_DCC_NON_BLOCKING

◆ DSCR_EXT_DCC_STALL_MODE

◆ DSCR_HALT_DBG_MODE

◆ DSCR_INSTR_COMP

◆ DSCR_INT_DIS

◆ DSCR_ITR_EN

◆ DSCR_MON_DBG_MODE

◆ DSCR_NON_SECURE

◆ DSCR_PIPE_ADVANCE

◆ DSCR_RUN_MODE

◆ DSCR_SEC_PRIV_INVASV_DIS

◆ DSCR_SEC_PRIV_NINVASV_DIS

◆ DSCR_STICKY_ABORT_IMPRECISE

◆ DSCR_STICKY_ABORT_PRECISE

◆ DSCR_STICKY_UNDEFINED

◆ OSLSR_NTT

◆ OSLSR_OSLK

◆ OSLSR_OSLM

| #define OSLSR_OSLM (OSLSR_OSLM0|OSLSR_OSLM1) |

◆ OSLSR_OSLM0

◆ OSLSR_OSLM1

◆ PRCR_DEBUG_NO_POWER_DOWN

◆ PRCR_HOLD_NON_DEBUG_RESET

◆ PRCR_WARM_RESET

◆ PRSR_DLK

◆ PRSR_HALTED

◆ PRSR_OSLK

◆ PRSR_POWERUP_STATUS

◆ PRSR_RESET_STATUS

◆ PRSR_STICKY_POWERDOWN_STATUS

◆ PRSR_STICKY_RESET_STATUS

Function Documentation

◆ arm_dpm_initialize()

| int arm_dpm_initialize | ( | struct arm_dpm * | dpm | ) |

Reinitializes DPM state at the beginning of a new debug session or after a reset which may have affected the debug module.

Definition at line 1114 of file arm_dpm.c.

References arm_dpm::arm, dpm_bp::bpwp, dpm_wp::bpwp, arm_dpm::bpwp_disable, arm_dpm::dbp, arm_dpm::dwp, ERROR_OK, LOG_WARNING, arm_dpm::nbp, dpm_bpwp::number, arm_dpm::nwp, arm::target, and target_name().

Referenced by arm11_dpm_init(), and cortex_a_dpm_setup().

◆ arm_dpm_modeswitch()

Definition at line 100 of file arm_dpm.c.

References arm_dpm::arm, ARM_MODE_ANY, ARMV4_5_MSR_GP, buf_get_u32(), arm::cpsr, ERROR_OK, arm_dpm::instr_cpsr_sync, arm_dpm::instr_write_data_r0, mode, and reg::value.

Referenced by arm_dpm_full_context(), arm_dpm_read_core_reg(), arm_dpm_write_core_reg(), arm_dpm_write_dirty_registers(), cortex_a_internal_restore(), cortex_a_post_debug_entry(), cortex_a_post_memaccess(), and cortex_a_prep_memaccess().

◆ arm_dpm_read_current_registers()

| int arm_dpm_read_current_registers | ( | struct arm_dpm * | dpm | ) |

Read basic registers of the current context: R0 to R15, and CPSR; sets the core mode (such as USR or IRQ) and state (such as ARM or Thumb).

In normal operation this is called on entry to halting debug state, possibly after some other operations supporting restore of debug state or making sure the CPU is fully idle (drain write buffer, etc).

Definition at line 333 of file arm_dpm.c.

References arm_dpm::arm, arm_dpm_read_reg(), arm_reg_current(), arm_set_cpsr(), ARMV4_5_MRS, arm::core_cache, arm::cpsr, reg::dirty, arm::dpm, ERROR_OK, arm_dpm::finish, arm_dpm::instr_read_data_r0, arm_dpm::prepare, reg_cache::reg_list, and reg::valid.

Referenced by arm11_debug_entry(), and cortex_a_debug_entry().

◆ arm_dpm_read_reg()

Definition at line 163 of file arm_dpm.c.

References arm_dpm::arm, ARM_STATE_ARM, ARM_STATE_JAZELLE, ARM_STATE_THUMB, ARM_STATE_THUMB_EE, ARM_VFP_V3_D0, ARM_VFP_V3_D31, ARM_VFP_V3_FPSCR, ARMV4_5_MCR, ARMV4_5_MRS, ARMV4_5_VMRS, buf_set_u32(), arm::core_state, reg::dirty, dpm_read_reg_u64(), ERROR_OK, arm_dpm::instr_read_data_dcc, arm_dpm::instr_read_data_r0, LOG_DEBUG, LOG_WARNING, reg::name, reg::valid, and reg::value.

Referenced by arm_dpm_full_context(), arm_dpm_read_core_reg(), arm_dpm_read_current_registers(), and cortex_a_debug_entry().

◆ arm_dpm_report_dscr()

| void arm_dpm_report_dscr | ( | struct arm_dpm * | dpm, |

| uint32_t | dcsr | ||

| ) |

Definition at line 1011 of file arm_dpm.c.

References arm_dpm::arm, DBG_REASON_BREAKPOINT, DBG_REASON_DBGRQ, DBG_REASON_UNDEFINED, DBG_REASON_WATCHPOINT, target::debug_reason, arm_dpm::dscr, DSCR_ENTRY, DSCR_ENTRY_BKPT_INSTR, DSCR_ENTRY_BREAKPOINT, DSCR_ENTRY_EXT_DBG_REQ, DSCR_ENTRY_HALT_REQ, DSCR_ENTRY_IMPRECISE_WATCHPT, DSCR_ENTRY_PRECISE_WATCHPT, and arm::target.

Referenced by arm11_check_init(), arm11_debug_entry(), and cortex_a_debug_entry().

◆ arm_dpm_report_wfar()

| void arm_dpm_report_wfar | ( | struct arm_dpm * | dpm, |

| uint32_t | wfar | ||

| ) |

Definition at line 987 of file arm_dpm.c.

References addr, arm_dpm::arm, ARM_STATE_AARCH64, ARM_STATE_ARM, ARM_STATE_JAZELLE, ARM_STATE_THUMB, ARM_STATE_THUMB_EE, arm::core_state, and arm_dpm::wp_addr.

Referenced by arm11_debug_entry(), and cortex_a_debug_entry().

◆ arm_dpm_setup()

| int arm_dpm_setup | ( | struct arm_dpm * | dpm | ) |

Hooks up this DPM to its associated target; call only once.

Initially this only covers the register cache.

Oh, and watchpoints. Yeah.

Definition at line 1049 of file arm_dpm.c.

References target_type::add_breakpoint, target_type::add_watchpoint, arm_dpm::arm, arm_build_reg_cache(), arm_dpm_full_context(), arm_dpm_read_core_reg(), arm_dpm_write_core_reg(), arm_free_reg_cache(), arm::core_cache, arm_dpm::dbp, arm_dpm::didr, arm::dpm, dpm_add_breakpoint(), dpm_add_watchpoint(), dpm_mcr(), dpm_mrc(), dpm_remove_breakpoint(), dpm_remove_watchpoint(), arm_dpm::dwp, ERROR_FAIL, ERROR_OK, arm::full_context, LOG_INFO, arm::mcr, arm::mrc, arm_dpm::nbp, arm_dpm::nwp, arm::read_core_reg, target::reg_cache, register_get_last_cache_p(), target_type::remove_breakpoint, target_type::remove_watchpoint, arm::target, target_name(), target::type, and arm::write_core_reg.

Referenced by arm11_dpm_init(), and cortex_a_dpm_setup().

◆ arm_dpm_write_dirty_registers()

| int arm_dpm_write_dirty_registers | ( | struct arm_dpm * | dpm, |

| bool | bpwp | ||

| ) |

Writes all modified core registers for all processor modes.

In normal operation this is called on exit from halting debug state.

- Parameters

-

dpm represents the processor bpwp true ensures breakpoints and watchpoints are set, false ensures they are cleared

Definition at line 441 of file arm_dpm.c.

References target_type::add_breakpoint, reg::arch_info, arm_dpm::arm, arm_dpm_modeswitch(), ARM_MODE_ANY, ARM_MODE_FIQ, ARM_MODE_USR, dpm_bp::bp, dpm_bp::bpwp, dpm_wp::bpwp, arm::core_cache, arm::core_mode, arm::cpsr, arm_dpm::dbp, reg::dirty, arm::dpm, dpm_add_breakpoint(), dpm_maybe_update_bpwp(), dpm_write_pc_core_state(), dpm_write_reg(), arm_dpm::dwp, ERROR_OK, reg::exist, arm_dpm::finish, breakpoint::is_set, watchpoint::is_set, arm_reg::mode, mode, arm_dpm::nbp, NULL, arm_reg::num, reg_cache::num_regs, arm_dpm::nwp, arm::pc, arm_dpm::prepare, reg_cache::reg_list, arm::target, target::type, and dpm_wp::wp.

Referenced by arm11_leave_debug_state(), and cortex_a_restore_context().