This represents an ARM Debug Interface (v5) Access Port (AP). More...

Data Fields | |

| uint64_t | ap_num |

| ADIv5: Number of this AP (0~255) ADIv6: Base address of this AP (4k aligned) TODO: to be more coherent, it should be renamed apsel. More... | |

| uint32_t | cfg_reg |

| bool | config_ap_never_release |

| uint32_t | csw_default |

| Default value for (MEM-AP) AP_REG_CSW register. More... | |

| uint32_t | csw_value |

| Cache for (MEM-AP) AP_REG_CSW register value. More... | |

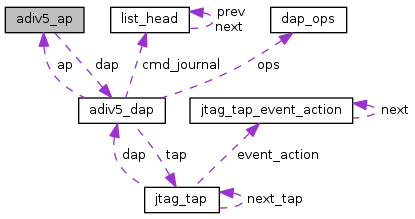

| struct adiv5_dap * | dap |

| DAP this AP belongs to. More... | |

| uint32_t | memaccess_tck |

| Configures how many extra tck clocks are added after starting a MEM-AP access before we try to read its status (and/or result). More... | |

| bool | packed_transfers |

| unsigned int | refcount |

| uint32_t | tar_autoincr_block |

| bool | tar_valid |

| target_addr_t | tar_value |

| Cache for (MEM-AP) AP_REG_TAR register value This is written to configure the address being read or written "-1" indicates no cached value. More... | |

| bool | unaligned_access_bad |

Detailed Description

This represents an ARM Debug Interface (v5) Access Port (AP).

Most common is a MEM-AP, for memory access.

Definition at line 243 of file arm_adi_v5.h.

Field Documentation

◆ ap_num

| uint64_t adiv5_ap::ap_num |

ADIv5: Number of this AP (0~255) ADIv6: Base address of this AP (4k aligned) TODO: to be more coherent, it should be renamed apsel.

Definition at line 254 of file arm_adi_v5.h.

Referenced by _dap_get_ap(), cortex_a_examine_first(), dap_find_get_ap(), dap_get_ap(), dap_get_config_ap(), dap_info_ap_header(), dap_info_mem_ap_header(), dap_instance_init(), dap_lookup_cs_component(), dap_lookup_cs_component_cs_component(), dap_put_ap(), dap_queue_ap_read(), dap_queue_ap_write(), jim_arm_tpiu_swo_enable(), jtag_ap_q_bankselect(), rshim_ap_q_read(), rtp_rom_loop(), stlink_dap_ap_read(), stlink_dap_ap_write(), stlink_dap_op_queue_ap_write(), stlink_usb_count_misc_rw_queue(), stlink_usb_misc_rw_segment(), stm32l4_probe(), stm32l4_read_idcode(), swd_queue_ap_bankselect(), and xtensa_dm_examine().

◆ cfg_reg

| uint32_t adiv5_ap::cfg_reg |

Definition at line 294 of file arm_adi_v5.h.

Referenced by COMMAND_HANDLER(), dap_get_debugbase(), dap_instance_init(), dap_put_ap(), is_64bit_ap(), and mem_ap_init().

◆ config_ap_never_release

| bool adiv5_ap::config_ap_never_release |

Definition at line 300 of file arm_adi_v5.h.

Referenced by dap_get_config_ap(), dap_instance_init(), and is_ap_in_use().

◆ csw_default

| uint32_t adiv5_ap::csw_default |

Default value for (MEM-AP) AP_REG_CSW register.

Definition at line 259 of file arm_adi_v5.h.

Referenced by COMMAND_HANDLER(), dap_instance_init(), dap_put_ap(), mem_ap_setup_csw(), stlink_dap_op_queue_ap_read(), and stlink_dap_op_queue_ap_write().

◆ csw_value

| uint32_t adiv5_ap::csw_value |

Cache for (MEM-AP) AP_REG_CSW register value.

This is written to configure an access mode, such as autoincrementing AP_REG_TAR during word access. "-1" indicates no cached value.

Definition at line 266 of file arm_adi_v5.h.

Referenced by COMMAND_HANDLER(), dap_invalidate_cache(), mem_ap_get_tar_increment(), mem_ap_init(), mem_ap_read_u32(), mem_ap_setup_csw(), mem_ap_write_u32(), stlink_dap_op_queue_ap_read(), and stlink_dap_op_queue_ap_write().

◆ dap

| struct adiv5_dap* adiv5_ap::dap |

DAP this AP belongs to.

Definition at line 247 of file arm_adi_v5.h.

Referenced by _dap_get_ap(), aarch64_examine_first(), ap_poll_register(), ap_read_register(), ap_write_register(), COMMAND_HANDLER(), cortex_a_init_debug_access(), cortex_m_assert_reset(), cortex_m_deassert_reset(), cortex_m_fast_read_all_regs(), dap_find_get_ap(), dap_get_ap(), dap_get_config_ap(), dap_get_debugbase(), dap_instance_init(), dap_is_multidrop(), dap_queue_ap_read(), dap_queue_ap_write(), handle_reset_halt(), jtag_ap_q_bankselect(), jtag_ap_q_read(), jtag_ap_q_write(), kinetis_ke_mdm_poll_register(), kinetis_ke_mdm_read_register(), kinetis_ke_mdm_write_register(), kinetis_mdm_poll_register(), kinetis_mdm_read_register(), kinetis_mdm_write_register(), mem_ap_init(), mem_ap_read(), mem_ap_read_atomic_u32(), mem_ap_read_tar(), mem_ap_read_u32(), mem_ap_setup_csw(), mem_ap_setup_tar(), mem_ap_write(), mem_ap_write_atomic_u32(), mem_ap_write_u32(), rshim_ap_q_read(), rshim_ap_q_write(), rtp_ap(), rtp_read_cs_regs(), rtp_rom_loop(), stlink_dap_ap_read(), stlink_dap_ap_write(), stlink_dap_op_queue_ap_read(), stlink_dap_op_queue_ap_write(), swd_queue_ap_bankselect(), swd_queue_ap_read(), swd_queue_ap_write(), vdebug_dap_queue_ap_read(), and vdebug_dap_queue_ap_write().

◆ memaccess_tck

| uint32_t adiv5_ap::memaccess_tck |

Configures how many extra tck clocks are added after starting a MEM-AP access before we try to read its status (and/or result).

Definition at line 279 of file arm_adi_v5.h.

Referenced by aarch64_examine_first(), COMMAND_HANDLER(), cortex_a_examine_first(), cortex_m_examine(), dap_instance_init(), dap_put_ap(), jtag_ap_q_read(), jtag_ap_q_write(), swd_queue_ap_read(), swd_queue_ap_write(), and xtensa_dm_examine().

◆ packed_transfers

| bool adiv5_ap::packed_transfers |

Definition at line 285 of file arm_adi_v5.h.

Referenced by mem_ap_init(), mem_ap_read(), and mem_ap_write().

◆ refcount

| unsigned int adiv5_ap::refcount |

Definition at line 297 of file arm_adi_v5.h.

Referenced by _dap_get_ap(), dap_cleanup_all(), dap_get_ap(), dap_get_config_ap(), dap_instance_init(), dap_put_ap(), dap_queue_ap_read(), dap_queue_ap_write(), and is_ap_in_use().

◆ tar_autoincr_block

| uint32_t adiv5_ap::tar_autoincr_block |

Definition at line 282 of file arm_adi_v5.h.

Referenced by cortex_m_examine(), dap_instance_init(), dap_put_ap(), mem_ap_read(), mem_ap_update_tar_cache(), mem_ap_write(), and xtensa_dm_examine().

◆ tar_valid

| bool adiv5_ap::tar_valid |

Definition at line 291 of file arm_adi_v5.h.

Referenced by COMMAND_HANDLER(), dap_invalidate_cache(), mem_ap_init(), mem_ap_read_tar(), mem_ap_setup_tar(), mem_ap_update_tar_cache(), stlink_dap_op_queue_ap_read(), and stlink_dap_op_queue_ap_write().

◆ tar_value

| target_addr_t adiv5_ap::tar_value |

Cache for (MEM-AP) AP_REG_TAR register value This is written to configure the address being read or written "-1" indicates no cached value.

Definition at line 273 of file arm_adi_v5.h.

Referenced by COMMAND_HANDLER(), mem_ap_read_tar(), mem_ap_setup_tar(), mem_ap_update_tar_cache(), stlink_dap_op_queue_ap_read(), and stlink_dap_op_queue_ap_write().

◆ unaligned_access_bad

| bool adiv5_ap::unaligned_access_bad |

Definition at line 288 of file arm_adi_v5.h.

Referenced by mem_ap_init(), mem_ap_read(), and mem_ap_write().

The documentation for this struct was generated from the following file: