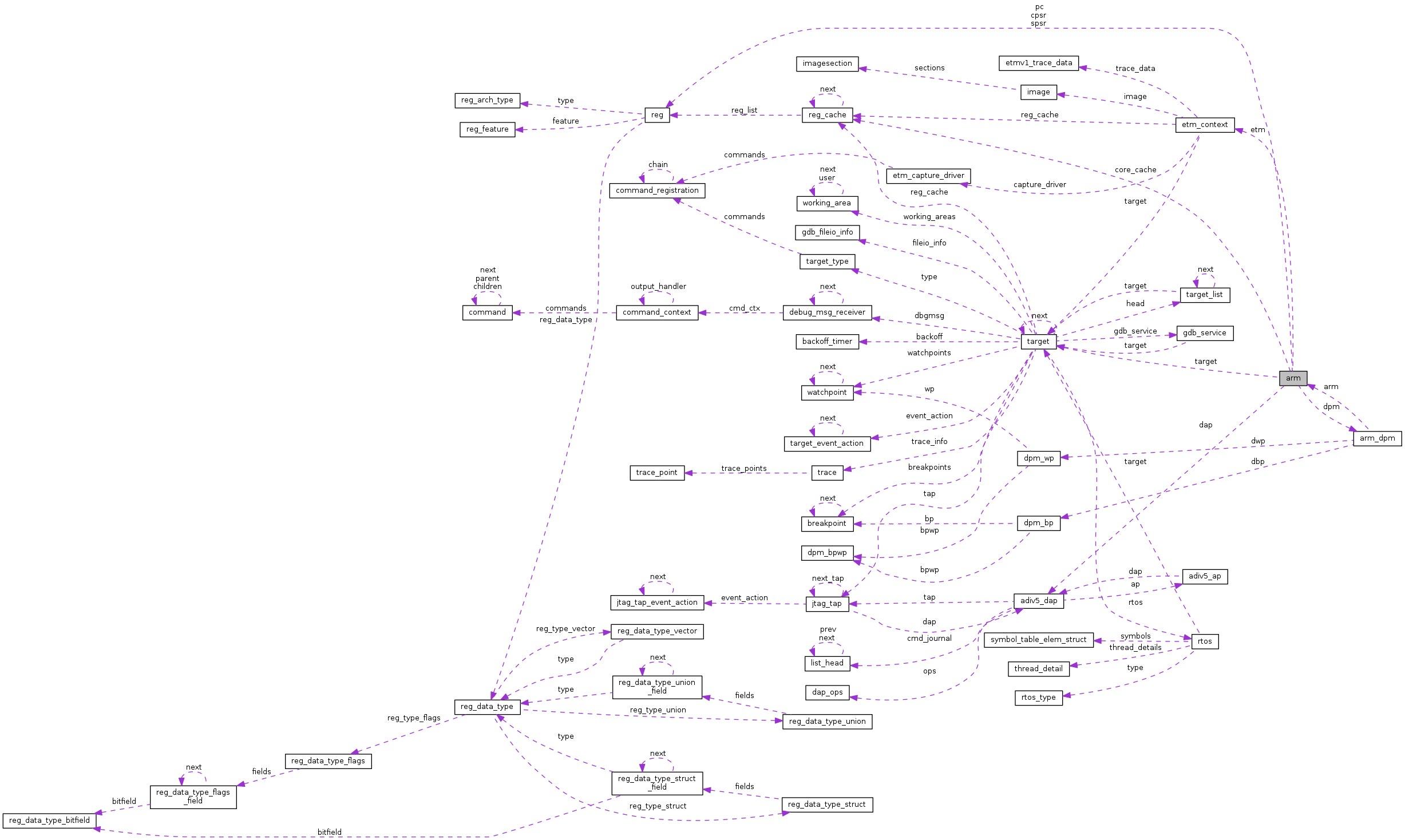

Represents a generic ARM core, with standard application registers. More...

Data Fields | |

| enum arm_arch | arch |

| ARM architecture version. More... | |

| void * | arch_info |

| int | arm_vfp_version |

| Floating point or VFP version, 0 if disabled. More... | |

| unsigned int | common_magic |

| struct reg_cache * | core_cache |

| enum arm_mode | core_mode |

| Record the current core mode: SVC, USR, or some other mode. More... | |

| enum arm_state | core_state |

| Record the current core state: ARM, Thumb, or otherwise. More... | |

| enum arm_core_type | core_type |

| Indicates what registers are in the ARM state core register set. More... | |

| struct reg * | cpsr |

| Handle to the CPSR/xPSR; valid in all core modes. More... | |

| struct adiv5_dap * | dap |

| For targets conforming to ARM Debug Interface v5, this handle references the Debug Access Port (DAP) used to make requests to the target. More... | |

| struct arm_dpm * | dpm |

| Handle for the debug module, if one is present. More... | |

| struct etm_context * | etm |

| Handle for the Embedded Trace Module, if one is present. More... | |

| int(* | full_context )(struct target *target) |

| Retrieve all core registers, for display. More... | |

| const int * | map |

| Support for arm_reg_current() More... | |

| int(* | mcr )(struct target *target, int cpnum, uint32_t op1, uint32_t op2, uint32_t crn, uint32_t crm, uint32_t value) |

| Write coprocessor register. More... | |

| int(* | mrc )(struct target *target, int cpnum, uint32_t op1, uint32_t op2, uint32_t crn, uint32_t crm, uint32_t *value) |

| Read coprocessor register. More... | |

| struct reg * | pc |

| Handle to the PC; valid in all core modes. More... | |

| int(* | read_core_reg )(struct target *target, struct reg *reg, int num, enum arm_mode mode) |

| Retrieve a single core register. More... | |

| int(* | setup_semihosting )(struct target *target, int enable) |

| struct reg * | spsr |

| Handle to the SPSR; valid only in core modes with an SPSR. More... | |

| struct target * | target |

| Backpointer to the target. More... | |

| int(* | write_core_reg )(struct target *target, struct reg *reg, int num, enum arm_mode mode, uint8_t *value) |

Detailed Description

Represents a generic ARM core, with standard application registers.

There are sixteen application registers (including PC, SP, LR) and a PSR. Cortex-M series cores do not support as many core states or shadowed registers as traditional ARM cores, and only support Thumb2 instructions.

Field Documentation

◆ arch

| enum arm_arch arm::arch |

ARM architecture version.

Definition at line 182 of file arm.h.

Referenced by arm720t_target_create(), arm9tdmi_target_create(), arm_blank_check_memory(), arm_checksum_memory(), arm_nandread(), arm_nandwrite(), armv4_5_run_algorithm_inner(), cortex_m_debug_entry(), cortex_m_examine(), cortex_m_has_tz(), cortex_m_read_memory(), cortex_m_write_memory(), riot_create(), and stm32lx_read_id_code().

◆ arch_info

| void* arm::arch_info |

Definition at line 233 of file arm.h.

Referenced by armv7a_init_arch_info(), armv7m_init_arch_info(), armv8_dpm_handle_exception(), armv8_dpm_modeswitch(), armv8_dpm_read_current_registers(), armv8_init_arch_info(), decode_cache_reg(), dpmv8_bpwp_disable(), dpmv8_dpm_prepare(), dpmv8_exec_opcode(), dpmv8_instr_cpsr_sync(), dpmv8_instr_read_data_dcc(), dpmv8_instr_read_data_dcc_64(), dpmv8_instr_read_data_r0(), dpmv8_instr_read_data_r0_64(), dpmv8_instr_write_data_dcc(), dpmv8_instr_write_data_dcc_64(), dpmv8_instr_write_data_r0(), dpmv8_instr_write_data_r0_64(), dpmv8_read_reg(), dpmv8_write_reg(), dragonite_target_create(), feroceon_assert_reset(), feroceon_branch_resume(), feroceon_branch_resume_thumb(), feroceon_bulk_write_memory(), feroceon_change_to_arm(), feroceon_common_setup(), feroceon_disable_single_step(), feroceon_enable_single_step(), feroceon_read_core_regs(), feroceon_read_core_regs_target_buffer(), feroceon_read_cp15(), feroceon_read_xpsr(), feroceon_set_dbgrq(), feroceon_target_create(), feroceon_write_core_regs(), feroceon_write_cp15(), feroceon_write_xpsr(), feroceon_write_xpsr_im8(), FLASH_BANK_COMMAND_HANDLER(), and xscale_init_arch_info().

◆ arm_vfp_version

| int arm::arm_vfp_version |

Floating point or VFP version, 0 if disabled.

Definition at line 197 of file arm.h.

Referenced by arm_build_reg_cache(), arm_get_gdb_reg_list(), and cortex_a_target_create().

◆ common_magic

| unsigned int arm::common_magic |

Definition at line 168 of file arm.h.

Referenced by arm_arch_state(), arm_init_arch_info(), armv7a_init_arch_info(), armv8_aarch64_state(), armv8_init_arch_info(), is_arm(), and xscale_arch_state().

◆ core_cache

| struct reg_cache* arm::core_cache |

Definition at line 170 of file arm.h.

Referenced by aarch64_assert_reset(), aarch64_restore_context(), adapter_debug_entry(), adapter_load_context(), adapter_resume(), adapter_step(), arm11_assert_reset(), arm11_debug_entry(), arm11_leave_debug_state(), arm11_read_memory_inner(), arm11_write_memory_inner(), arm7_9_assert_reset(), arm7_9_full_context(), arm7_9_restore_context(), arm7_9_resume(), arm7_9_soft_reset_halt(), arm7_9_step(), arm7tdmi_branch_resume_thumb(), arm920t_read_cp15_interpreted(), arm920t_write_cp15_interpreted(), arm9tdmi_branch_resume_thumb(), arm_build_reg_cache(), arm_dpm_full_context(), arm_dpm_read_current_registers(), arm_dpm_setup(), arm_dpm_write_dirty_registers(), arm_free_reg_cache(), arm_full_context(), arm_get_gdb_reg_list(), arm_reg_current(), arm_semihosting(), arm_set_cpsr(), armv4_5_get_reg(), armv4_5_get_reg_mode(), armv4_5_run_algorithm_inner(), armv4_5_set_reg(), armv4_5_set_reg_mode(), armv7m_arch_state(), armv7m_build_reg_cache(), armv7m_free_reg_cache(), armv7m_get_gdb_reg_list(), armv7m_read_core_reg(), armv7m_restore_context(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv7m_write_core_reg(), armv8_build_reg_cache(), armv8_dpm_full_context(), armv8_dpm_handle_exception(), armv8_dpm_read_core_reg(), armv8_dpm_read_current_registers(), armv8_dpm_setup(), armv8_dpm_write_core_reg(), armv8_dpm_write_dirty_registers(), armv8_get_core_reg32(), armv8_get_gdb_reg_list(), armv8_read_reg_simdfp_aarch32(), armv8_reg_current(), armv8_write_reg_simdfp_aarch32(), COMMAND_HANDLER(), cortex_a_assert_reset(), cortex_a_internal_restart(), cortex_a_internal_restore(), cortex_m_assert_reset(), cortex_m_debug_entry(), cortex_m_endreset_event(), cortex_m_examine(), cortex_m_fast_read_all_regs(), cortex_m_poll(), cortex_m_resume(), cortex_m_slow_read_all_regs(), cortex_m_soft_reset_halt(), cortex_m_step(), feroceon_branch_resume_thumb(), feroceon_bulk_write_memory(), hl_assert_reset(), post_result(), xscale_deassert_reset(), xscale_debug_entry(), xscale_full_context(), xscale_restore_banked(), xscale_resume(), and xscale_step_inner().

◆ core_mode

| enum arm_mode arm::core_mode |

Record the current core mode: SVC, USR, or some other mode.

Definition at line 182 of file arm.h.

Referenced by aarch64_mmu_modify(), aarch64_post_debug_entry(), aarch64_restore_system_control_reg(), adapter_debug_entry(), arm7_9_debug_entry(), arm7_9_full_context(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm920t_read_cp15_interpreted(), arm920t_write_cp15_interpreted(), arm_arch_state(), arm_dpm_write_dirty_registers(), arm_get_gdb_reg_list(), arm_semihosting(), arm_set_cpsr(), armv4_5_get_reg_mode(), armv4_5_run_algorithm_inner(), armv4_5_set_reg_mode(), armv7a_arch_state(), armv7m_arch_state(), armv7m_get_core_reg(), armv7m_start_algorithm(), armv7m_wait_algorithm(), armv8_aarch64_state(), armv8_dpm_read_current_registers(), armv8_get_core_reg(), armv8_get_core_reg32(), armv8_identify_cache(), armv8_mmu_translate_va_pa(), armv8_read_mpidr(), armv8_set_cpsr(), COMMAND_HANDLER(), cortex_a_post_debug_entry(), cortex_m_debug_entry(), post_result(), and xscale_debug_entry().

◆ core_state

| enum arm_state arm::core_state |

Record the current core state: ARM, Thumb, or otherwise.

Definition at line 182 of file arm.h.

Referenced by __attribute__(), aarch64_read_cpu_memory(), aarch64_read_cpu_memory_fast(), aarch64_read_cpu_memory_slow(), aarch64_restore_one(), aarch64_write_cpu_memory(), aarch64_write_cpu_memory_slow(), arm11_nextpc(), arm7_9_debug_entry(), arm7_9_resume(), arm7_9_soft_reset_halt(), arm7_9_step(), arm_arch_state(), arm_dpm_read_reg(), arm_dpm_report_wfar(), arm_semihosting(), arm_set_cpsr(), armv4_5_get_mode(), armv4_5_run_algorithm_inner(), armv7m_init_arch_info(), armv8_aarch64_state(), armv8_get_gdb_arch(), armv8_get_gdb_reg_list(), armv8_set_cpsr(), COMMAND_HANDLER(), cortex_a_internal_restore(), cortex_a_step(), dpmv8_instr_read_data_r0_64(), dpmv8_instr_write_data_r0_64(), feroceon_bulk_write_memory(), and post_result().

◆ core_type

| enum arm_core_type arm::core_type |

Indicates what registers are in the ARM state core register set.

Definition at line 182 of file arm.h.

Referenced by arm11_examine(), arm11_target_create(), arm_build_reg_cache(), arm_get_gdb_reg_list(), arm_init_arch_info(), armv7m_init_arch_info(), COMMAND_HANDLER(), cortex_a_examine_first(), and xscale_init_arch_info().

◆ cpsr

| struct reg* arm::cpsr |

Handle to the CPSR/xPSR; valid in all core modes.

Definition at line 176 of file arm.h.

Referenced by adapter_debug_entry(), arm720t_soft_reset_halt(), arm7_9_full_context(), arm7_9_read_core_reg(), arm7_9_read_memory(), arm7_9_restore_context(), arm7_9_soft_reset_halt(), arm7_9_write_core_reg(), arm7_9_write_memory(), arm920t_soft_reset_halt(), arm926ejs_soft_reset_halt(), arm_arch_state(), arm_build_reg_cache(), arm_dpm_modeswitch(), arm_dpm_read_current_registers(), arm_dpm_write_dirty_registers(), arm_get_gdb_reg_list(), arm_set_cpsr(), armv4_5_get_cpsr(), armv4_5_run_algorithm_inner(), armv7m_arch_state(), armv7m_build_reg_cache(), armv8_aarch64_state(), armv8_build_reg_cache(), armv8_dpm_modeswitch(), armv8_set_cpsr(), cortex_m_debug_entry(), cortex_m_resume(), post_result(), xscale_resume(), and xscale_step_inner().

◆ dap

| struct adiv5_dap* arm::dap |

For targets conforming to ARM Debug Interface v5, this handle references the Debug Access Port (DAP) used to make requests to the target.

Definition at line 239 of file arm.h.

Referenced by aarch64_examine_first(), aarch64_init_arch_info(), COMMAND_HANDLER(), cortex_a_examine_first(), cortex_a_init_arch_info(), cortex_m_endreset_event(), cortex_m_examine(), cortex_m_examine_exception_reason(), and cortex_m_init_arch_info().

◆ dpm

| struct arm_dpm* arm::dpm |

Handle for the debug module, if one is present.

Definition at line 205 of file arm.h.

Referenced by aarch64_read_cpu_memory(), aarch64_read_cpu_memory_fast(), aarch64_read_cpu_memory_slow(), aarch64_write_cpu_memory(), aarch64_write_cpu_memory_slow(), arm11_check_init(), arm11_debug_entry(), arm_dpm_full_context(), arm_dpm_read_core_reg(), arm_dpm_read_current_registers(), arm_dpm_setup(), arm_dpm_write_core_reg(), arm_dpm_write_dirty_registers(), arm_semihosting(), armv7a_identify_cache(), armv7a_l1_d_cache_clean_inval_all(), armv7a_l1_d_cache_clean_virt(), armv7a_l1_d_cache_flush_virt(), armv7a_l1_d_cache_inval_virt(), armv7a_l1_i_cache_inval_all(), armv7a_l1_i_cache_inval_virt(), armv7a_mmu_translate_va_pa(), armv7a_read_midr(), armv7a_read_mpidr(), armv7a_read_ttbcr(), armv7a_show_fault_registers(), armv8_cache_d_inner_clean_inval_all(), armv8_cache_d_inner_flush_level(), armv8_cache_d_inner_flush_virt(), armv8_cache_i_inner_inval_virt(), armv8_dpm_full_context(), armv8_dpm_read_core_reg(), armv8_dpm_read_current_registers(), armv8_dpm_setup(), armv8_dpm_write_core_reg(), armv8_dpm_write_dirty_registers(), armv8_identify_cache(), armv8_read_mpidr(), armv8_show_fault_registers32(), dpm_add_breakpoint(), dpm_add_watchpoint(), dpm_mcr(), dpm_mrc(), dpm_remove_breakpoint(), dpm_remove_watchpoint(), dpmv8_add_breakpoint(), dpmv8_add_watchpoint(), dpmv8_mcr(), dpmv8_mrc(), dpmv8_remove_breakpoint(), and dpmv8_remove_watchpoint().

◆ etm

| struct etm_context* arm::etm |

Handle for the Embedded Trace Module, if one is present.

Definition at line 208 of file arm.h.

Referenced by arm11_examine(), arm7_9_examine(), COMMAND_HANDLER(), and etm_setup().

◆ full_context

Retrieve all core registers, for display.

Definition at line 213 of file arm.h.

Referenced by arm_dpm_setup(), arm_init_arch_info(), armv8_dpm_setup(), COMMAND_HANDLER(), and xscale_init_arch_info().

◆ map

| const int* arm::map |

Support for arm_reg_current()

Definition at line 182 of file arm.h.

Referenced by adapter_debug_entry(), arm_reg_current(), arm_set_cpsr(), and cortex_m_debug_entry().

◆ mcr

| int(* arm::mcr) (struct target *target, int cpnum, uint32_t op1, uint32_t op2, uint32_t crn, uint32_t crm, uint32_t value) |

Write coprocessor register.

Definition at line 228 of file arm.h.

Referenced by arm720t_init_arch_info(), arm920t_init_arch_info(), arm926ejs_init_arch_info(), arm_dpm_setup(), arm_init_arch_info(), armv8_dpm_setup(), cortex_a_mmu_modify(), cortex_a_post_memaccess(), cortex_a_prep_memaccess(), and cortex_a_restore_cp15_control_reg().

◆ mrc

| int(* arm::mrc) (struct target *target, int cpnum, uint32_t op1, uint32_t op2, uint32_t crn, uint32_t crm, uint32_t *value) |

Read coprocessor register.

Definition at line 222 of file arm.h.

Referenced by arm720t_init_arch_info(), arm920t_init_arch_info(), arm926ejs_init_arch_info(), arm_dpm_setup(), arm_init_arch_info(), armv8_dpm_setup(), and cortex_a_post_debug_entry().

◆ pc

| struct reg* arm::pc |

Handle to the PC; valid in all core modes.

Definition at line 173 of file arm.h.

Referenced by aarch64_restore_one(), adapter_debug_entry(), adapter_poll(), adapter_resume(), adapter_step(), arm11_nextpc(), arm720t_soft_reset_halt(), arm7_9_enable_eice_step(), arm7_9_restore_context(), arm7_9_resume(), arm7_9_soft_reset_halt(), arm7_9_step(), arm7tdmi_branch_resume_thumb(), arm920t_soft_reset_halt(), arm926ejs_soft_reset_halt(), arm9tdmi_branch_resume_thumb(), arm_arch_state(), arm_build_reg_cache(), arm_dpm_write_dirty_registers(), arm_semihosting(), armv4_5_run_algorithm_completion(), armv7m_arch_state(), armv7m_build_reg_cache(), armv7m_wait_algorithm(), armv8_aarch64_state(), armv8_build_reg_cache(), armv8_dpm_modeswitch(), cortex_a_internal_restore(), cortex_a_step(), cortex_m_debug_entry(), cortex_m_resume(), cortex_m_step(), feroceon_branch_resume_thumb(), feroceon_bulk_write_memory(), post_result(), xscale_debug_entry(), xscale_read_trace(), xscale_resume(), xscale_step(), and xscale_step_inner().

◆ read_core_reg

Retrieve a single core register.

Definition at line 216 of file arm.h.

Referenced by adapter_load_context(), arm_dpm_setup(), arm_init_arch_info(), armv4_5_get_core_reg(), armv4_5_run_algorithm_inner(), armv7m_get_core_reg(), armv7m_init_arch_info(), armv8_dpm_setup(), armv8_get_core_reg(), armv8_get_core_reg32(), cortex_m_slow_read_all_regs(), and xscale_init_arch_info().

◆ setup_semihosting

Definition at line 199 of file arm.h.

Referenced by arm_semihosting_init(), armv7a_init_arch_info(), armv7m_init_arch_info(), and armv8_init_arch_info().

◆ spsr

| struct reg* arm::spsr |

Handle to the SPSR; valid only in core modes with an SPSR.

Definition at line 179 of file arm.h.

Referenced by arm7_9_debug_entry(), arm7_9_write_core_reg(), arm_semihosting(), arm_set_cpsr(), cortex_a_debug_entry(), post_result(), and xscale_debug_entry().

◆ target

| struct target* arm::target |

Backpointer to the target.

Definition at line 202 of file arm.h.

Referenced by arm11_add_debug_inst(), arm11_add_debug_scan_n(), arm11_add_ir(), arm11_check_init(), arm11_debug_entry(), arm11_examine(), arm11_leave_debug_state(), arm11_read_dscr(), arm11_run_instr_data_from_core(), arm11_run_instr_data_to_core(), arm11_run_instr_data_to_core_noack(), arm11_sc7_run(), arm11_write_dscr(), arm_dpm_initialize(), arm_dpm_report_dscr(), arm_dpm_setup(), arm_dpm_write_dirty_registers(), arm_init_arch_info(), armv7a_init_arch_info(), armv8_dpm_initialize(), armv8_dpm_report_dscr(), armv8_dpm_setup(), armv8_dpm_write_dirty_registers(), armv8_init_arch_info(), armv8_read_mpidr(), cortex_a_bpwp_disable(), cortex_a_bpwp_enable(), cortex_a_dpm_prepare(), cortex_a_instr_cpsr_sync(), cortex_a_instr_read_data_dcc(), cortex_a_instr_read_data_r0(), cortex_a_instr_read_data_rt_dcc(), cortex_a_instr_write_data_dcc(), cortex_a_instr_write_data_r0(), cortex_a_instr_write_data_rt_dcc(), cortex_a_read_dcc(), dpm_maybe_update_bpwp(), and dpmv8_maybe_update_bpwp().

◆ write_core_reg

| int(* arm::write_core_reg) (struct target *target, struct reg *reg, int num, enum arm_mode mode, uint8_t *value) |

Definition at line 218 of file arm.h.

Referenced by arm_dpm_setup(), armv7m_init_arch_info(), armv7m_restore_context(), armv8_dpm_setup(), and xscale_init_arch_info().

The documentation for this struct was generated from the following file: